AXI Bridge for PCI Express v2.4

8

PG055 June 4, 2014

Chapter 2

Product Specification

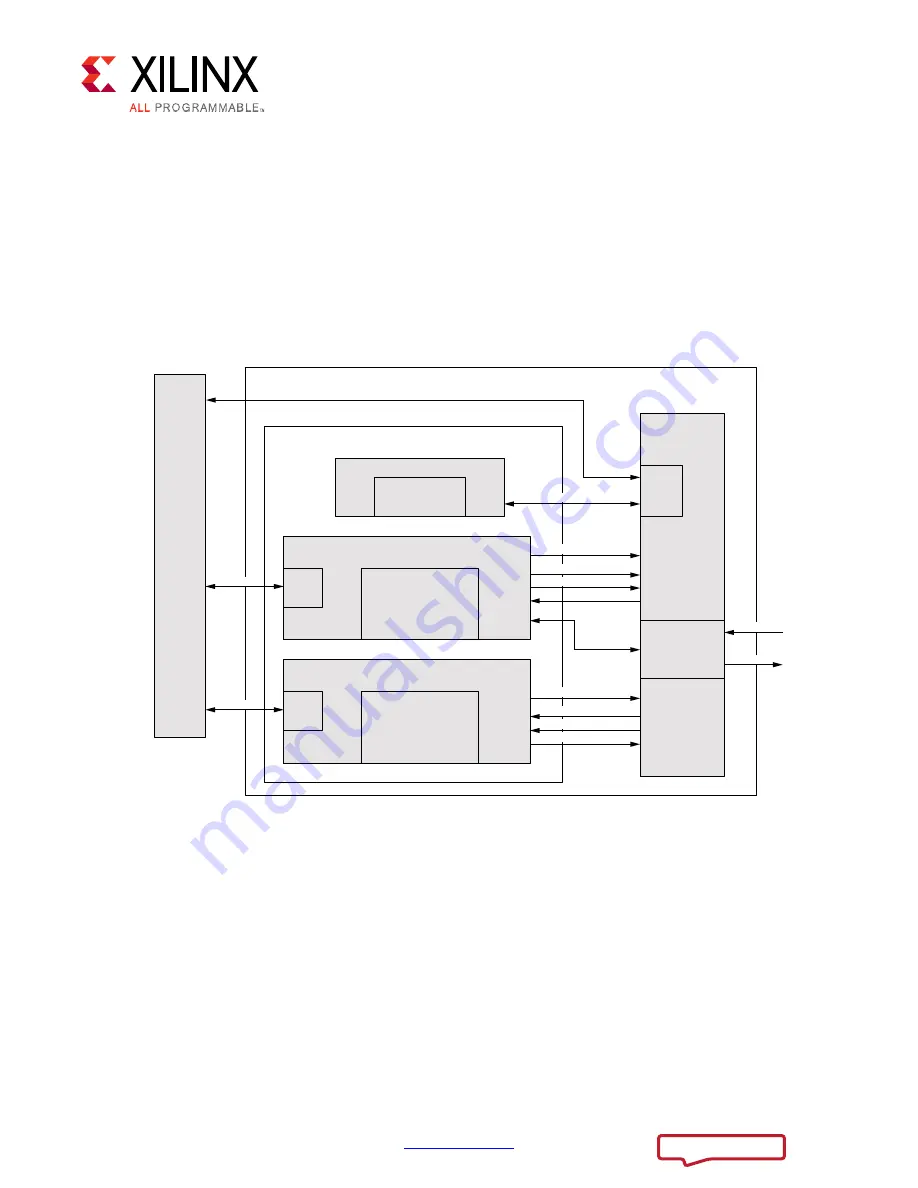

shows the architecture of the AXI Bridge for PCI Express® core.

The Register block contains registers used in the AXI Bridge for PCI Express core for

dynamically mapping the AXI4 memory mapped (MM) address range provided using the

AXIBAR parameters to an address for PCIe range.

The Slave Bridge provides termination of memory-mapped AXI4 transactions from an AXI

master device (such as a processor). The Slave Bridge provides a way to translate addresses

that are mapped within the AXI4 memory mapped address domain to the domain addresses

for PCIe. When a remote AXI master initiates a write transaction to the Slave Bridge, the

write address and qualifiers are captured and write data is queued in a first in first out

(FIFO). These are then converted into one or more MemWr TLPs, depending on the

X-Ref Target - Figure 2-1

Figure 2-1:

AXI Bridge for PCI Express Architecture

5HJLVWHU%ORFN

0DVWHU%ULGJH

$;,3&,H%ULGJH

6ODYH%ULGJH

$;,6

(QKDQFHG3&,H

$;,65HT0HP:U

$;,6&RPS0HP5G

%ORFN,)

3&,H5[

3&,H7[

3&,H+DUG

%ORFN

$;,/LWH

,)

$;,

6ODYH

,)

$;,

0DVWHU

,)

$;,

0HPRU\

0DSSHG

%XV

$;,3&,H

7UDQVODWLRQ

9HFWRUV

7/3+HDGHU*HQHUDWLRQ

$GGUHVV7UDQVODWLRQ

5DQJH&KHFNIRU

VHJPHQWDWLRQ

(UURU+DQGOLQJ

7/3+HDGHU([WUDFWLRQ

$GGUHVV7UDQVODWLRQ

0DVWHU&PG*HQHUDWLRQ

(UURU+DQGOLQJ

$;,00

$;,00

$;,00

$;,/LWH,3,&

6ODYH,QWUSW6WUEV

$;,006%ULGJH

$;,6&RPS0HP:U

$;,6&RPS&SOG

0DVWHU,QWUSW6WUEV

$;,65HT0HP5G

$;,65HT&SOG