NINA-W1 series - System integration manual

UBX-17005730 - R15

System description

Page 12 of 54

C1 - Public

1.7.2.1

RMII Startup precautions

The

RMII_CLK

input (GPIO27) is multiplexed with the ESP boot pin. Therefore, to ensure that the boot

mode is not entered inadvertently, the

RMII_CLK

(GPIO27) must be held high during boot for at least

1.5 ms.

When using u-connectXpress, the

RMII_CLK

pin is monitored during boot. The u-connectXpress

software checks the availability of the clock signal 1.2 s after boot. You must make sure to that the

RMII_CLK

signal is available at that time to enable the RMII interface. The clock signal can be enabled

beforehand, but only if the requirement to avoid entering the ESP boot mode is not interfered with.

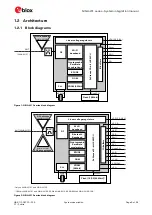

On EVK-NINA-W1, these startup precautions are implemented using two buffers and a RC delay

circuit that override the RMII clock from the PHY. This delays the clock so that it starts a short time

(50 ms) after the module boot.

Figure 4: EVK-NINA-W1 RMII clock delay circuit

1.7.2.2

MAC to PHY connection

When connecting NINA-W1 series modules to an external PHY circuit, both the RMII and SMI

interfaces must be connected. The default PHY address (0x1) must be configured on the PHY side.

Follow the recommendations of your chosen PHY chip supplier for implementation details.

An example of a PHY implementation is shown in Figure 5. PHY KSZ8081 is recommended and is used

on the EVK-NINA-W1.