NEO-M8P - Hardware Integration Manual

UBX-15028081 - R05

Early Production Information

Hardware description

Page 7 of 27

Module

VDD_USB

LDO

VDD_USB

R4

USB_DP

USB_DM

R5

C24

C23

D2

VBUS

DP

DM

GND

U

S

B

D

e

vi

c

e Co

n

n

ec

to

r

U1

EN

R11

EN

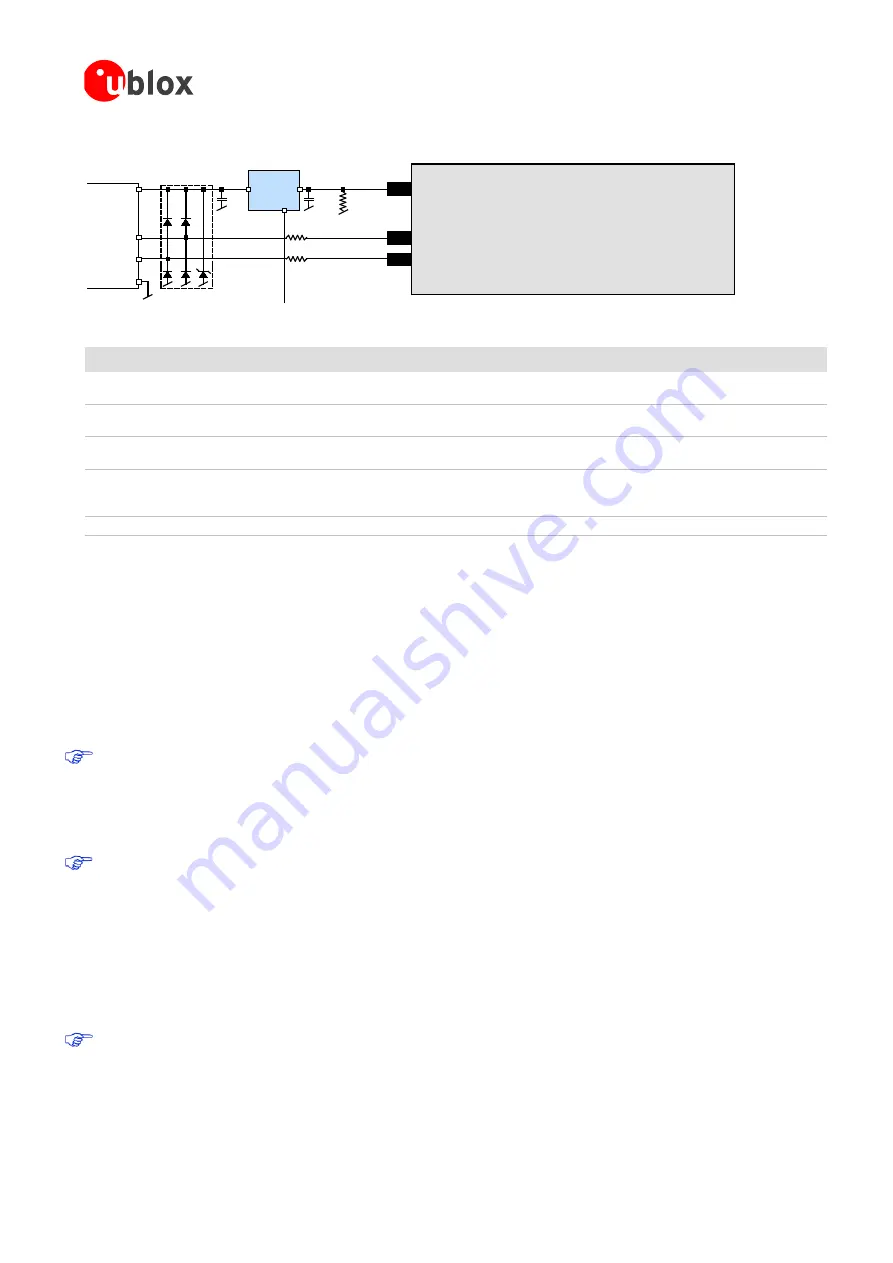

Figure 2: USB Interface

Name Component

Function

Comments

U1

LDO

Regulates VBUS (4.4 …5.25 V)

down to a voltage of 3.3 V.

Almost no current requirement (~1 mA) if the GNSS receiver is operated as a

USB self-powered device.

C23,

C24

Capacitors

Required according to the specification of LDO U1

D2

Protection

diodes

Protect circuit from overvoltage

/ ESD when connecting.

Use low capacitance ESD protection such as ST Microelectronics USBLC6-2.

R4, R5 Serial

termination

resistors

Establish a full-speed driver

impedance of 28…44

Ω

A value of 27

Ω

is recommended.

R11

Resistor

100 k

Ω

is recommended.

Table 1: Summary of USB external components

1.4.3

Display Data Channel (DDC)

An I

2

C compatible Display Data Channel (DDC) interface is available with NEO-M8P modules for serial

communication with an external host CPU. The interface operates in slave mode only (master mode is not

supported). The DDC protocol and electrical interface are fully compatible with the Fast-Mode of the I

2

C industry

standard. DDC pins

SDA

and

SCL

have internal pull-up resistors.

For more information about the DDC implementation, see the

u-blox 8 / u-blox M8 Receiver Description Including

Protocol Specification

[2]. For bandwidth information, see the

NEO-M8P Data Sheet

[1]. For timing parameters

consult the

I

2

C-bus specification

The NEO-M8P DDC interface supports serial communication with u-blox cellular modules. See the

specification of the applicable cellular module to confirm compatibility.

1.4.4

SPI

An SPI interface is optionally available for communication to a host CPU.

SPI is not available in the default configuration, because its pins are shared with the UART and DDC

interfaces. The SPI interface can be enabled by connecting

D_SEL

to ground. For speed and clock

frequency, see the

NEO-M8P Data Sheet

1.4.5

TX Ready signal

The TX Ready signal indicates that the receiver has data to transmit. A listener can wait on the TX Ready signal

instead of polling the DDC or SPI interfaces. The UBX-CFG-PRT message enables configuration of signal polarity

and buffer threshold (in bytes) before the TX Ready signal goes active. The TX Ready signal can be mapped to

UART TXD (PIO 06). The TX Ready function is disabled by default.

The TX Ready functionality can be enabled and configured by AT commands sent to the u-blox cellular

module supporting the feature. For more information, see the

GPS Implementation and Aiding Features