22.2 Detail of Flash Memory

In on-board programming, the CPU executes commands for reprogramming or erasing Flash memory. This reprog-

ramming/erase control program should be prepared by the user beforehand. Since Flash memory content cannot

be read while Flash memory is being written or erased, it is necessary to run the reprogram/erase control program

on the built-in RAM. Do not generate interrupt/fault except reset to avoid abnormal program termination.

22.2.1 Function

Flash memory is generally compliant with the JEDEC standards except for some specific functions. Howev-

er; a method of address designation of operation command is different from standard commands.

If write/erase operation is executed, commands are input to flash memory using 32-bit (1-word) store instruc-

tion command. After command input, write or erase operation is automatically executed in inside.

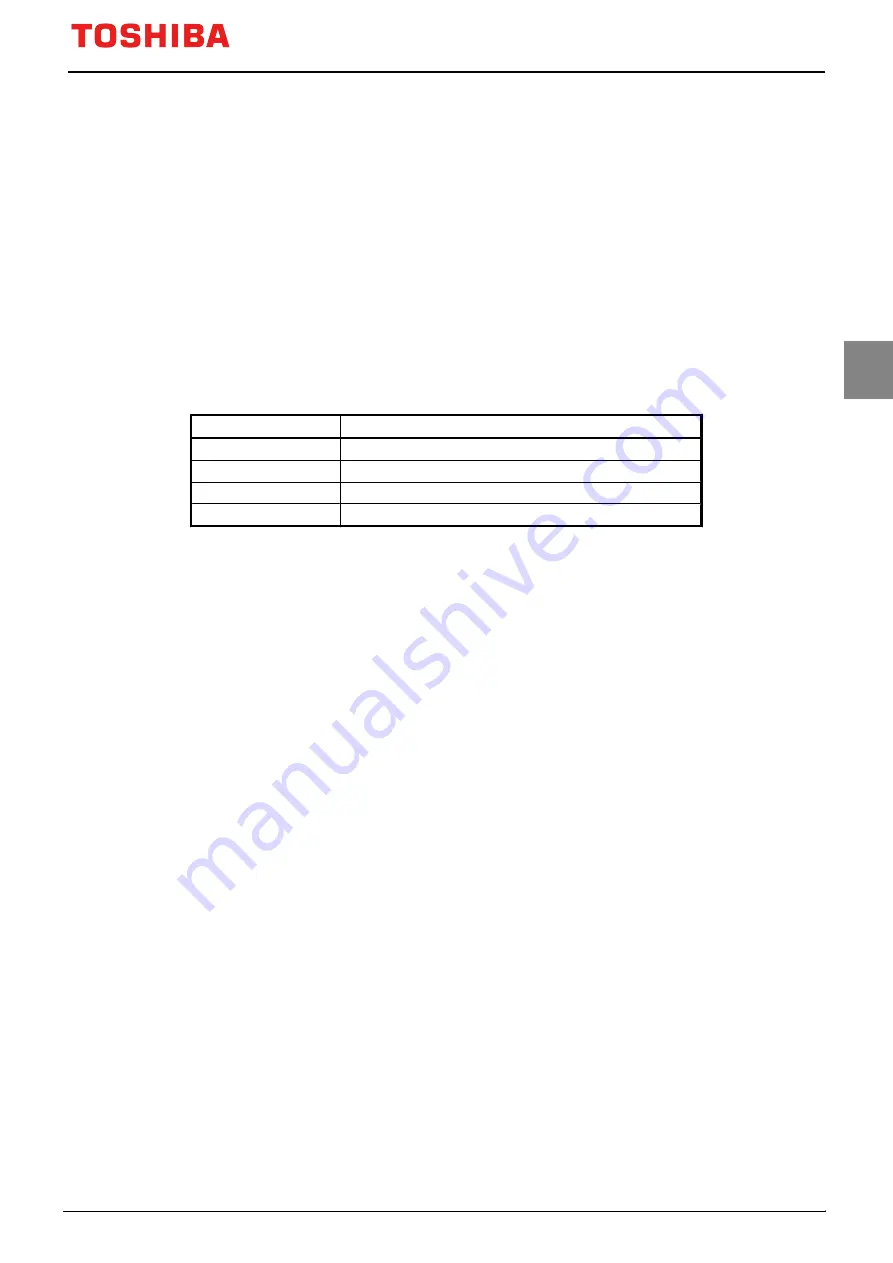

Table 22-4 Flash memory function

Main function

Description

Automatic page program

Writes data automatically.

Automatic chip erase

Erases the entire area of Flash memory automatically.

Automatic block erase

Erases a selected block automatically.

Write/erase protect

The write or erase operation can be individually inhibited for each block.

Note:

In

TMPM3V6/M3V4

, after Flash programming or Flash Erasing ,it should be Clearing Instruction buffer.

Pls refer "22.1.6.3 FCCR (Flash Interface control register)" for a clear method.

Note:

Check the FCSR<RDY_BSY> to make sure each command sequence end such as Flash writing,

Flash Erase, Protection bit program, Protection bit Erase. and then hold for 200 μs or more before read-

ing data from Flash memory or starting instruction fetch.

22.2.2 Operation Mode of Flash Memory

Flash memory provides mainly two types of operation modes;

・

The mode to read memory data (Read mode)

・

The mode to erase or rewrite memory data automatically (Automatic operation mode)

After power-on, after rest or after automatic operation mode is finished normally, Flash memory becomes

read mode. Instruction stored in Flash memory or data read is executed in the read mode.

If commands is input during the read mode, the operation mode becomes the automatic operation. If the com-

mand process is normally finished, the operation mode returns to the read mode except the ID-Read com-

mand. During the automatic operation, data read and instruction execution stored in Flash memory cannot be

performed.

If command process is abnormally finished then the operation mode should forcibly return to read mode.

In this case, use the read command, read/reset command or hardware reset.

22.2.3 Hardware Reset

A hardware reset means a power-on reset or warm reset to use returning to the read mode when the automat-

ic programming/erase operation is forcibly cancelled, or automatic operation abnormally ends.

If the hardware reset occurs during the automatic operation, Flash memory stops the automatic operation

and returns to the read mode. If a hardware reset is generated during Flash memory automatic program/erase

operation, the hardware reset needs 0.5 μs or more reset period regardless of system clock. At this time, it

takes approximately 2 ms until enabling to read after reset. Note that if a hardware reset occurs during the au-

tomatic operation, data write operation is not executed properly. Set write operation again.

TMPM3V6/M3V4

Page 453

2019-02-06

Содержание TMPM3V4

Страница 1: ...32 Bit RISC Microcontroller TX03 Series TMPM3V6 M3V4 ...

Страница 2: ... 2019 Toshiba Electronic Devices Storage Corporation ...

Страница 7: ...Revision History Date Revision Comment 2019 02 06 1 First Release ...

Страница 8: ......

Страница 22: ...xiv ...

Страница 52: ...TMPM3V6 M3V4 3 Processor Core 3 6 Exclusive access Page 30 2019 02 06 ...

Страница 148: ...TMPM3V6 M3V4 7 Exceptions 7 6 Exception Interrupt Related Registers Page 126 2019 02 06 ...

Страница 178: ...TMPM3V6 M3V4 9 Input Output port 9 2 Block Diagrams of Ports Page 156 2019 02 06 ...

Страница 206: ...TMPM3V6 M3V4 10 16 bit Timer Event Counters TMRB 10 7 Applications using the Capture Function Page 184 2019 02 06 ...

Страница 232: ...TMPM3V6 M3V4 11 Universal Asynchronous Receiver Transmitter Circuit UART 11 4 Operation Description Page 210 2019 02 06 ...

Страница 354: ...TMPM3V6 M3V4 14 Synchronous Serial Port SSP 14 6 Frame Format Page 332 2019 02 06 ...

Страница 419: ...TMPM3V6 M3V4 Page 397 2019 02 06 ...

Страница 420: ...TMPM3V6 M3V4 16 Analog Digital Converter ADC 16 6 Timing chart of AD conversion Page 398 2019 02 06 ...

Страница 462: ...TMPM3V6 M3V4 21 Watchdog Timer WDT 21 5 Control register Page 440 2019 02 06 ...

Страница 510: ...TMPM3V6 M3V4 22 Flash Memory Operation 22 4 Programming in the User Boot Mode Page 488 2019 02 06 ...

Страница 538: ...TMPM3V6 M3V4 25 Electrical Characteristics 25 7 Recommended Oscillation Circuit Page 516 2019 02 06 ...

Страница 541: ...26 3 TMPM3V4FWUG TMPM3V4FSUG Type LQFP64 P 1010 0 50E LPHQVLRQV TMPM3V6 M3V4 Page 519 2019 02 06 ...

Страница 544: ......