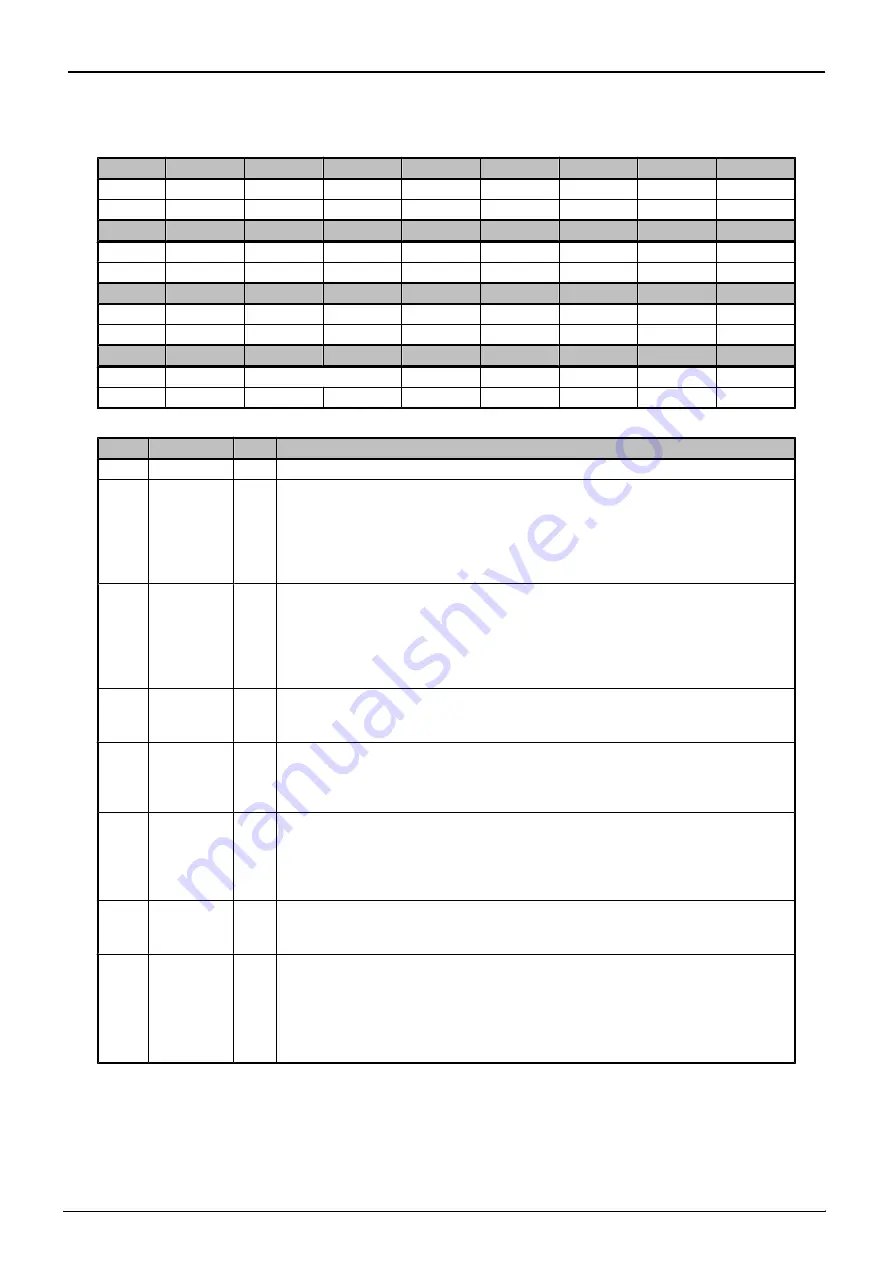

11.3.8 UARTxLCR_H (UART Line Control Register)

31

30

29

28

27

26

25

24

Bit symbol

-

-

-

-

-

-

-

-

After reset

0

0

0

0

0

0

0

0

23

22

21

20

19

18

17

16

Bit symbol

-

-

-

-

-

-

-

-

After reset

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

Bit symbol

-

-

-

-

-

-

-

-

After reset

0

0

0

0

0

0

0

0

7

6

5

4

3

2

1

0

Bit symbol

SPS

WLEN

FEN

STP2

EPS

PEN

BRK

After reset

0

0

0

0

0

0

0

0

Bit

Bit symbol

Type

Function

31-8

−

R

Read as "0".

7

SPS

R/W

Selects a stick parity

0: A stick parity is disabled.

1: When <EPS> = "0", "1" is sent/received as a parity bit.

When <EPS> = "1", "0" is sent/received as a parity bit.

<SPS> has no meaning when <PEN> is set to "0" and the parity check and generation are disabled.

For details of the truth table of <SPS>, <EPS>, and <PEN>, refer to Table 11-1.

6-5

WLEN[1:0]

R/W

Word length

00: 5 bits

01: 6 bits

10: 7 bits

11: 8 bits

These bits indicate the number of data bits transmitted/received in the frame.

4

FEN

R/W

Enables/disables the FIFO.

0: The FIFO is disabled (The FIFO becomes a 1-deep hold register.)

1: The FIFO is enabled

3

STP2

R/W

Selects a transmission stop bit length

0: 1 bit

1: 2 bits

In reception, a 2-bit length stop bit is not checked.

2

EPS

R/W

Even parity selection

0: Odd parity

1: Even parity

Controls a parity bit in transmission/reception.

When <PEN> is set to "0", if parity check and generation are disabled, this bit has no meaning.

1

PEN

R/W

Parity enable

0: Disabled (Parity is disabled. A parity bit is not added.)

1: Enabled (Parity check and generation are enabled.)

0

BRK

R/W

Enables/disables break transmission

0: No break transmission

1: Performs break transmission

When <BRK> is set to "1", "Low" level signal is output to UTxTXD output after currently ongoing transmis-

sion is complete. To establish break state, <BRK> must be keep "1" at least for two-frame transmission pe-

riod. If break state is established, the contents of the transmit FIFO is not influenced. When break state is

not transmitted, set "0" to <BRK>.

Note:

When the contents of UARTxIBRD or UARTxFBRD are updated, UARTxLCR_H always must be writ-

ten at the end of writing process.

TMPM3V6/M3V4

11. Universal Asynchronous Receiver-Transmitter Circuit (UART)

11.3 Registers

Page 194

2019-02-06

Содержание TMPM3V4

Страница 1: ...32 Bit RISC Microcontroller TX03 Series TMPM3V6 M3V4 ...

Страница 2: ... 2019 Toshiba Electronic Devices Storage Corporation ...

Страница 7: ...Revision History Date Revision Comment 2019 02 06 1 First Release ...

Страница 8: ......

Страница 22: ...xiv ...

Страница 52: ...TMPM3V6 M3V4 3 Processor Core 3 6 Exclusive access Page 30 2019 02 06 ...

Страница 148: ...TMPM3V6 M3V4 7 Exceptions 7 6 Exception Interrupt Related Registers Page 126 2019 02 06 ...

Страница 178: ...TMPM3V6 M3V4 9 Input Output port 9 2 Block Diagrams of Ports Page 156 2019 02 06 ...

Страница 206: ...TMPM3V6 M3V4 10 16 bit Timer Event Counters TMRB 10 7 Applications using the Capture Function Page 184 2019 02 06 ...

Страница 232: ...TMPM3V6 M3V4 11 Universal Asynchronous Receiver Transmitter Circuit UART 11 4 Operation Description Page 210 2019 02 06 ...

Страница 354: ...TMPM3V6 M3V4 14 Synchronous Serial Port SSP 14 6 Frame Format Page 332 2019 02 06 ...

Страница 419: ...TMPM3V6 M3V4 Page 397 2019 02 06 ...

Страница 420: ...TMPM3V6 M3V4 16 Analog Digital Converter ADC 16 6 Timing chart of AD conversion Page 398 2019 02 06 ...

Страница 462: ...TMPM3V6 M3V4 21 Watchdog Timer WDT 21 5 Control register Page 440 2019 02 06 ...

Страница 510: ...TMPM3V6 M3V4 22 Flash Memory Operation 22 4 Programming in the User Boot Mode Page 488 2019 02 06 ...

Страница 538: ...TMPM3V6 M3V4 25 Electrical Characteristics 25 7 Recommended Oscillation Circuit Page 516 2019 02 06 ...

Страница 541: ...26 3 TMPM3V4FWUG TMPM3V4FSUG Type LQFP64 P 1010 0 50E LPHQVLRQV TMPM3V6 M3V4 Page 519 2019 02 06 ...

Страница 544: ......