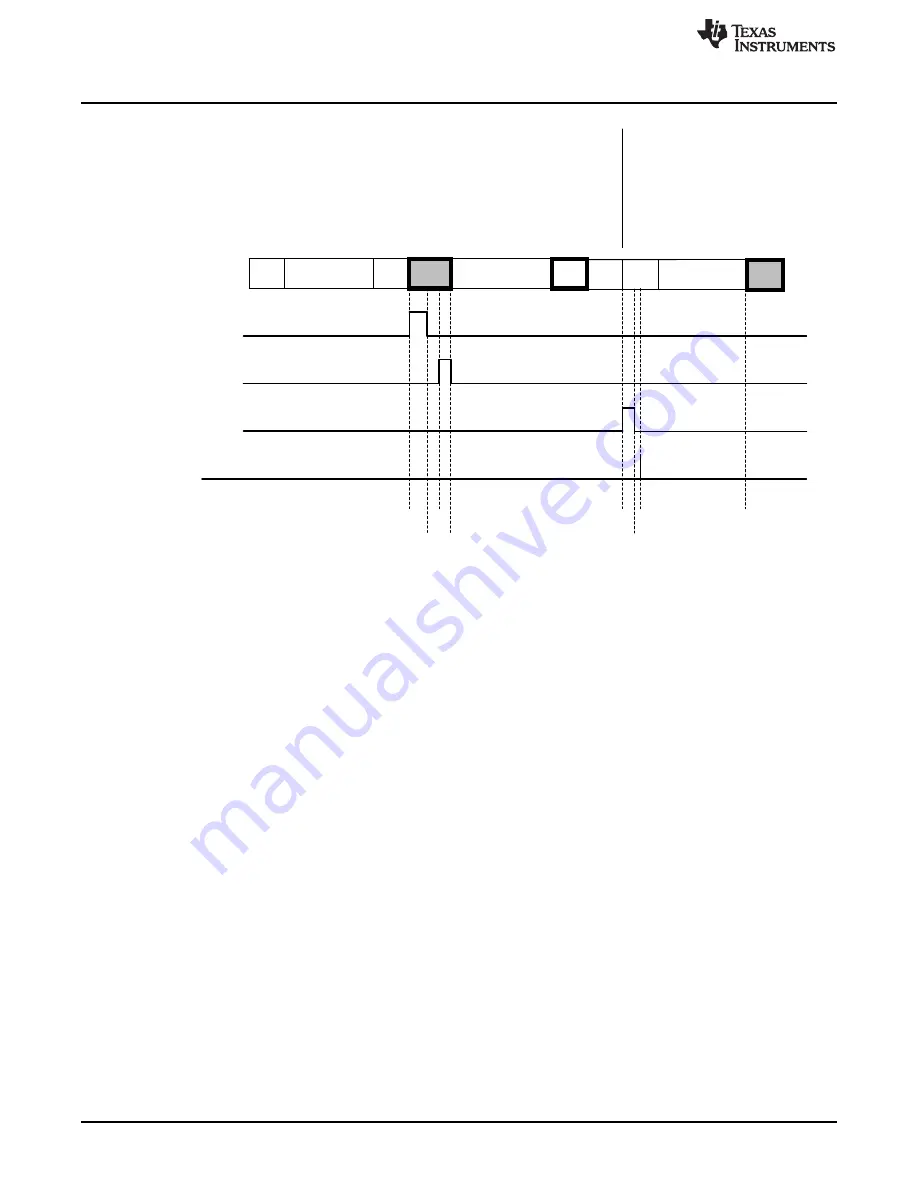

S

Address Rd

A

1

7

Data Byte

8

A

P

1

1

1

1

DATA_REQUEST

Write to TXBUF

EOM

1

S

Address

1

7

A

1

First Message Second Message

8

Write to ACK

3

2

5

1

6

7

4

PMBus Slave Mode Command Examples

362

SNIU028A – February 2016 – Revised April 2016

Copyright © 2016, Texas Instruments Incorporated

PMBus Interface/I2C Interface

Figure 10-10. Simple Read with Full Automation

1. DATA_REQUEST is set t

DREQ1

nanoseconds after the falling edge of the clock for the last bit of the

address.

2. The firmware reads from PMBST, clearing the DATA_REQUEST bit. Since one byte is being sent out,

the firmware needs to make sure that TX_COUNT is set to 1.

3. Next the firmware needs to write the byte to TXBUF. It takes ttxbwrite ns after the write for any clock

stretching of the ACK to be ended. If the firmware is fast enough, no clock stretching will occur.

4. As soon as the data starts being transmitted, the TXBUF is transferred to the shift register

5. The EOM bit will be set t

EOM

ns after the falling edge of the data line indicating the stop signal.

6. The firmware needs to read the PMBST register, which will clear the EOM bit.

7. Then the firmware needs to write to the ACK register. This is just an internal ACK to tell the interface

that the EOM has been detected. The ACK bit is cleared immediately, since there is no wait for an

external ACK to complete.

8. Like the write message, there is no clock stretch until a valid address is detected. If the ACK is written

to before this, there is no clock stretch at all.

Note that the A with a 1 below and with no grey background means a NACK from the master, which is

appropriate for the last byte of a read message.

10.3.9 Simple Read of 4 Bytes with Full Automation

Up to 4 bytes can be read with the same number of firmware steps as 1 byte, taking advantage of the 4

byte TXBUF. Here is a sequence diagram for 4 bytes: