Low Voltage Test Procedure Example

18

SLUUC64 – June 2020

Copyright © 2020, Texas Instruments Incorporated

UCC5870QDWJEVM-026 Evaluation Module User’s Guide

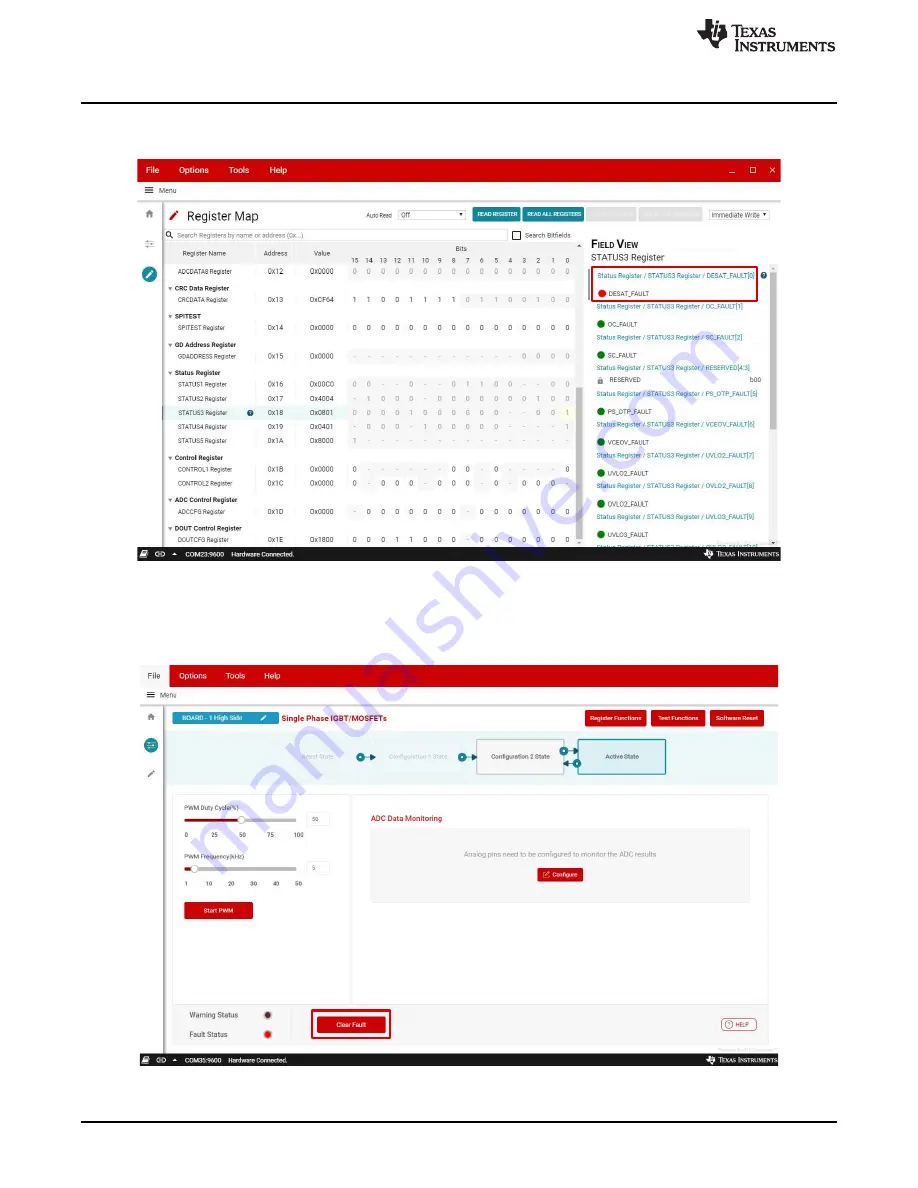

18. When there is a fault, read all status register and find out which fault was triggered in register map.

In the above example, it can be found that DESAT_FAULT is triggered.

Figure 21. Status Register Shows DESAT Fault

19. The fault can be reset by clicking "Clear fault" which writes 1 to CONTROL2 register bit[15]. Please

note ADC fault (Status 5 Register bit[15]) is on with default setting which selects external Vref for ADC

but the EVM board doesn't have external Vref, this fault can be cleared by selecting internal Vref.

Figure 22. Clear Fault Option