8

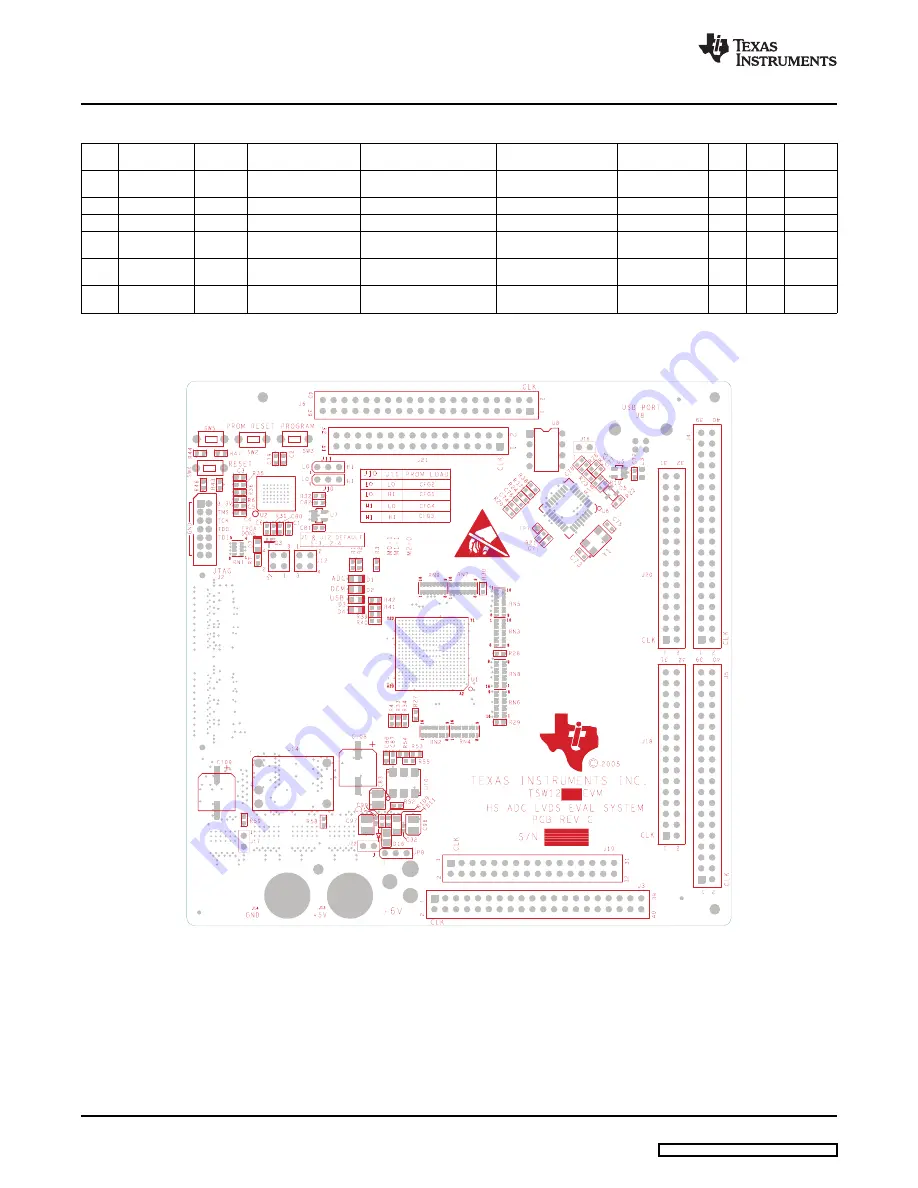

Circuit Board Layout and Layer Stackup

Circuit Board Layout and Layer Stackup

www.ti.com

Table 1. Bill of Materials (continued)

QTY

Reference

Not

Part

Foot Print

Part Number

Manufacturer

Tol

Volt

Wat

Installed

1

U12

TPS76701QPWP

HTSSOP_20_260x177_26_pwr

TPS76701QPWP

TI

TI Provide

pad

1

U14

PTH03000W

SMD_PWRMOD_EUT5

PTH03000WAS

TI

TI Provide

1

U15

TPS73225-SOT23

DBV5

TPS73225DBVT

TI

TI Provide

1

Y1

12MHz w/ 18pF

smd_xtal_AMB3B

ABM3B-12.000MHZ-10-1-

Abracon

U-T

4

Screw 4-40 X 3/8"

PMS 440 0038 PH

Building Fasteners

PCB

legs

4

Standoff RD 4-40 THR

1846

Keystone

0.875" ALUM

Figure 18. TSW1200C Layout Top Layer

30

TSW1200EVM: High-Speed LVDS Deserializer and Analysis System

SLAU212A – April 2007 – Revised August 2008