OCP

master (INTC)

AXI2OCP_FCLK

MPU_RST

AXI slave

OCP master

(L3)

AXI2OCP

OCP2.0 (64 bit)

No OCP

I2Async

I2ASYNC_CLK

To ARM

AXI (64 bit)

MPU subsystem

To INTC

OCP2.0 (32 bit)

Levelshift

T2Async

L3

Preliminary

MPU Subsystem

www.ti.com

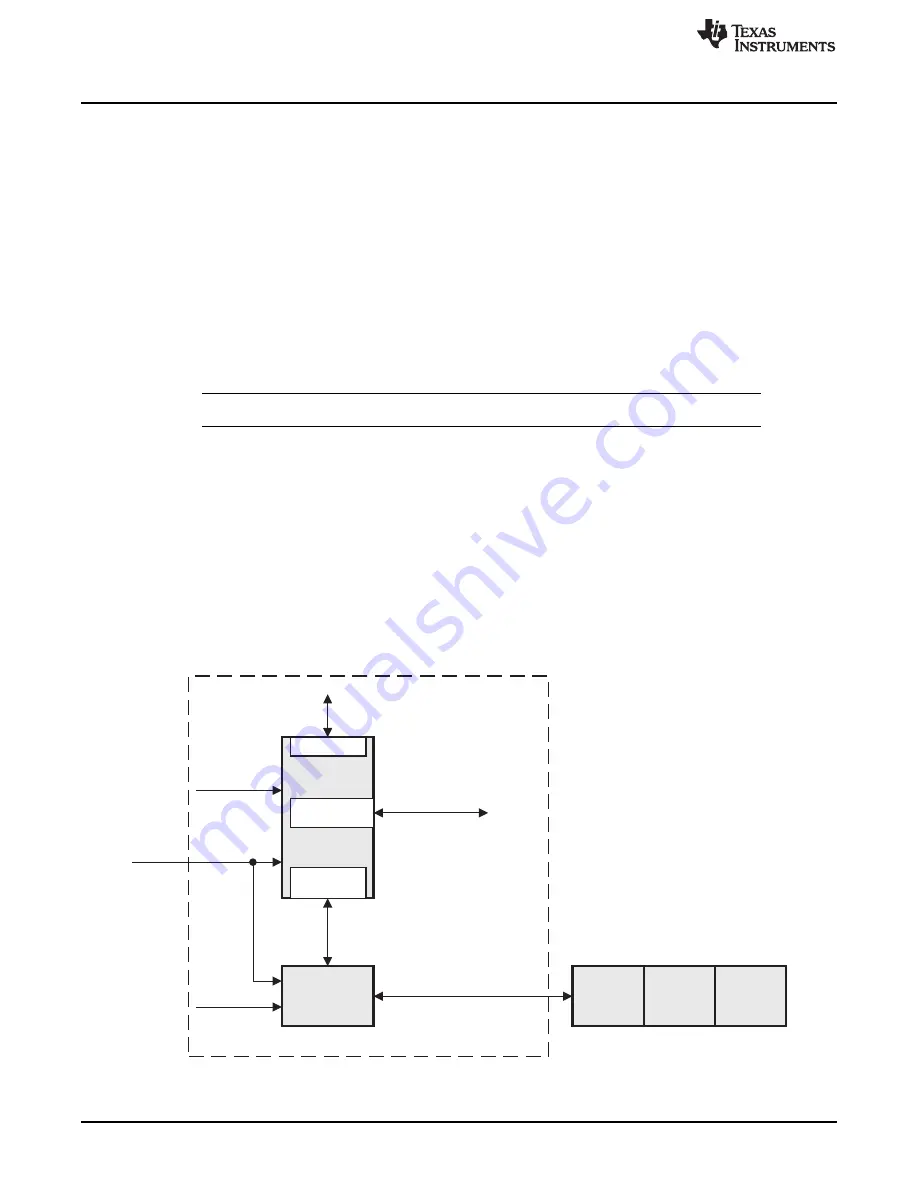

1.2.6 AXI2OCP and I2Async Bridges

1.2.6.1

Bridges Overview

The AXI2OCP Bridge is used to connect the AXI bus on the ARM A8 to the OCP native L3 interconnect

(64-bit width), EMIF OCP port (128-bit width), interrupt controller and security state-machine. It converts

between AXI and OCP protocols and maintains a mapping of AXI tags to the OCP Tag ID. A memory

region must be reserved for the interrupt handler. The bridge is required to do some minimal address

decoding to decide where to forward the requests.

The AXI2OCP Bridge and the target modules (EMIF, L3) operate in different clock domains. The interface

between the AXI2OCP Bridge and EMIF/L3 must go through an asynchronous bridge to properly

synchronize signals to the opposite clock domain.

Bridging to the L3 is accomplished through an asynchronous interface involving the I2Async and T2Async

modules. The I2Async module inside the MPU subsystem has an OCP port that is asynchronously

transferred to the T2Async module and routed to the L3. T2Async is outside the MPU subsystem.

NOTE:

The interface between I2Async and T2Async is not an OCP protocol.

1.2.6.2

Key Features

•

Targets 500 MHz operating frequency in C014.P at an operating voltage of 1.0V.

•

Connects to the EMIF via a 128-bit OCP port and asynchronous bridge.

•

Connects to the L3 interconnect via a 64-bit OCP port and asynchronous bridge.

•

Connects to the interrupt controller via a 32-bit OCP port. (Only single transactions are supported)

•

Supports Single-Request-Multiple-Data (data handshaking) burst mode to pipeline requests.

•

Supports multiple outstanding requests.

•

Security, emulation, and boot-mode translation support.

•

Exclusive accesses are translated to non-exclusive read/write in the bridge.

Figure 1-5. Overview of the AXI2OCP and the L3 Bridges

102

Chip Level Resources

SPRUGX9 – 15 April 2011

© 2011, Texas Instruments Incorporated

Содержание TMS320C6A816 Series

Страница 2: ...Preliminary 2 SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 92: ...92 Read This First SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1122: ...1122 Multichannel Audio Serial Port McASP SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1562: ...1562 Real Time Clock RTC SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1658: ...1658 Timers SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1750: ...1750 UART IrDA CIR Module SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...

Страница 1984: ...1984 Universal Serial Bus USB SPRUGX9 15 April 2011 Submit Documentation Feedback 2011 Texas Instruments Incorporated...