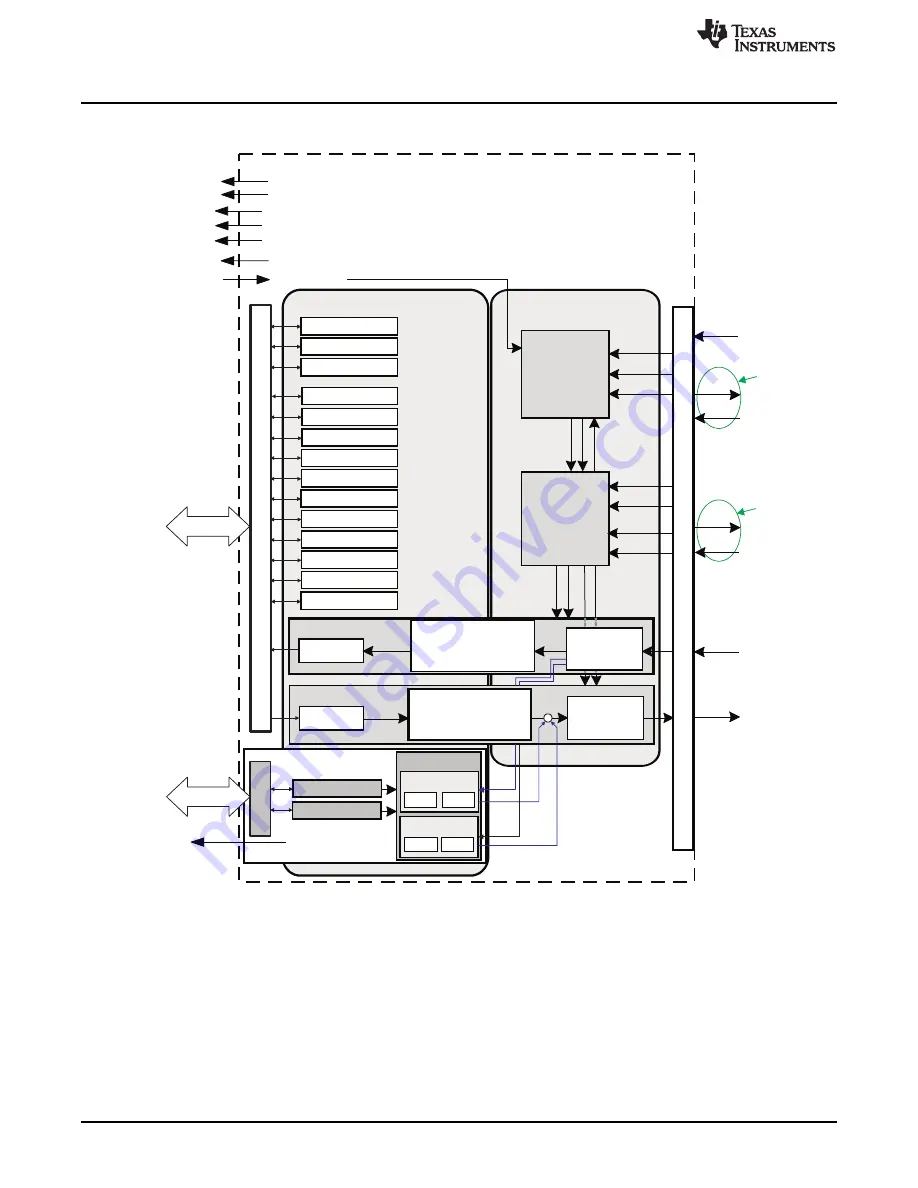

SIDETONE core

Transmitter

Receiver

McBSP3

Registers for data,

clock and

frame-synchronization

control and monitoring

Registers for

multichannel control

and monitoring

2 SPCR_REGs

2 RCR_REGs

2 XCR_REGs

2 SRGR_REGs

PCR_REG

2 MCR_REGs

8 RCER_REGs

8 XCER_REGs

Transmit shift

register

(XSR)

RINTCLR_REG

ROVFLCLR_REG

2 THRSH_REGs

RCCR_REG

DXR_REG

DRR_REG

XINTCLR_REG

XCCR_REG

DX

DR

CLKS

CLKXO

CLKXI

CLKX

FSXO

FSXI

FSX

Interface clock domain

Functional clock domain

{

{

SGAINCR_REG

ST_McBSP3_IRQ

Data processing unit

Ch1 process

GAIN

FIR

Ch0 process

GAIN

FIR

Receive buffer (RB)

FIFO (128

32 bit words)

×

SFIRCR_REG

Receive shift

register

(RSR)

{

Interrupt

to CPU

Synchronization

events to DMA

controller

McBSP3_IRQ_TX

McBSP3_IRQ_RX

McBSP3_IRQ

McBSP3_DMA_RX

McBSP3_DMA_TX

McBSP3_ICLK

McBSP3_SWAKEUP

PRCM

Interrupt

to CPU

Sample rate

generator

CLKX

CLKR

FS generated

CLK generated

CLKR

FSR

FSX

CLKX

CLKS

Clock and

frame logic

FSX_int

FSR_int

FSR_int

CLKR_int

CLKX_int

L4

interconnect

L

4

in

terface

L

4

in

terface

L4

interconnect

Transmit buffer (XB)

FIFO (128

32 bit words)

×

mcbsp-023

Pin block

Public Version

McBSP Functional Description

www.ti.com

Figure 21-23. McBSP3 Block Diagram

21.4.2 McBSP Data Transfer Process

For McBSP1, McBSP3, McBSP4, and McBSP5 modules, receive and transmit operations are

triple-buffered (512 bytes buffers organized in 32-bit words are used).

For the McBSP2 module, receive and transmit operations are quadruple-buffered (5K bytes buffers

organized in 32-bit words are used). Receive and transmit buffers are separated in two memories: The

same buffer as the others McBSP modules (1K bytes) and an audio buffer (4K bytes). The audio buffer is

the largest one and is clocked by the interface clock, while the other buffer is used for synchronizing data

to/from the audio buffer with the functional transmit/receive clock domains.

shows this

implementation in the McBSP2 data transfer paths.

3092

Multi-Channel Buffered Serial Port

SWPU177N – December 2009 – Revised November 2010

Copyright © 2009–2010, Texas Instruments Incorporated

Содержание OMAP36 Series

Страница 174: ...174 List of Tables SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 692: ...692 MPU Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 1084: ...1084 IVA2 2 Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 1990: ...1990 2D 3D Graphics Accelerator SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2334: ...2334 Memory Subsystem SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2700: ...2700 Memory Management Units SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2868: ...2868 HDQ 1 Wire SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 2974: ...2974 UART IrDA CIR SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3054: ...3054 Multichannel SPI SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3462: ...3462 MMC SD SDIO Card Interface SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3508: ...3508 General Purpose Interface SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3584: ...3584 Initialization SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...

Страница 3648: ...3648 Debug and Emulation SWPU177N December 2009 Revised November 2010 Copyright 2009 2010 Texas Instruments Incorporated ...