registers. J33 is used to select the PMIC IO voltage, either 1.8 V or 3.3 V. The fifth header is J24 which allows

VCCA to be powered from the USB connection and the configuration of GPIO2, I2C2 or SPI.

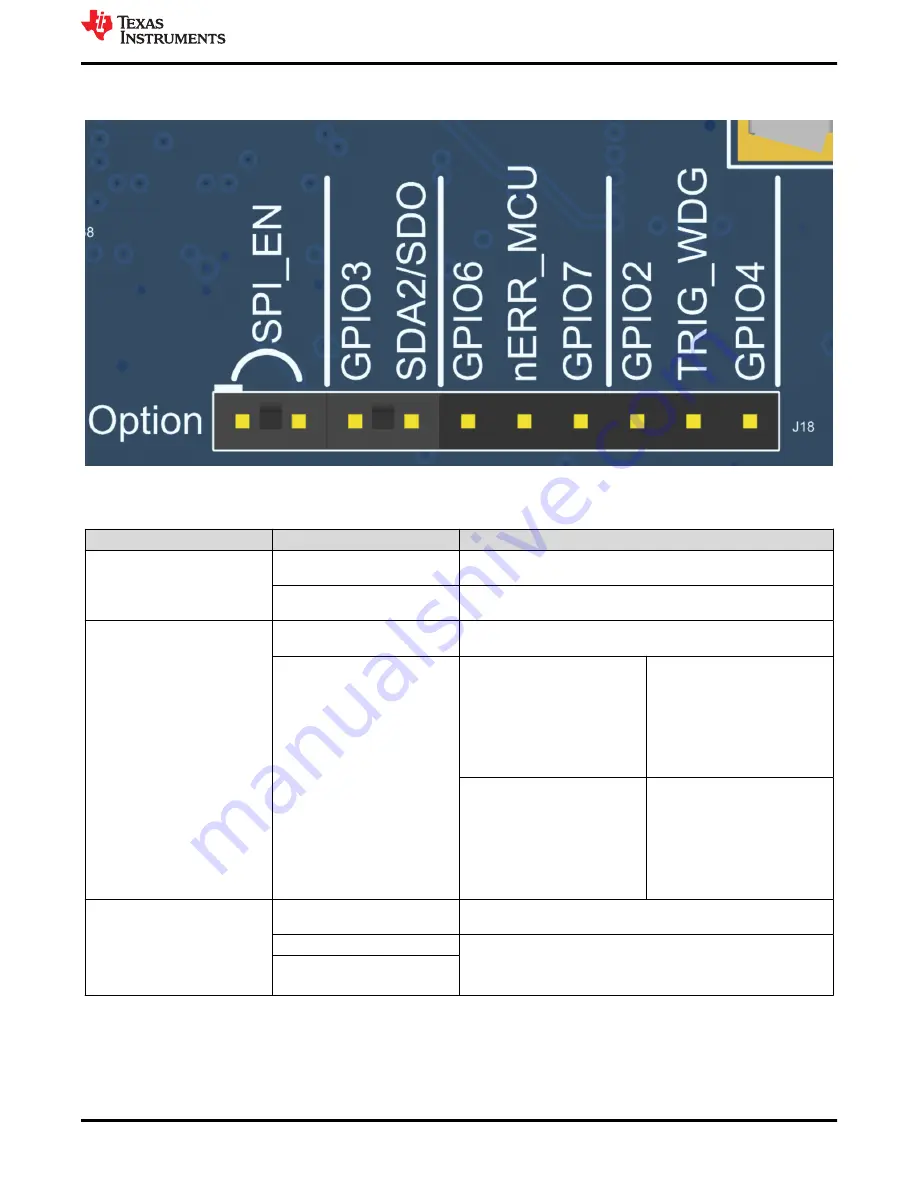

Figure 3-1. EVM Header J18

Table 3-3. Header J18 Description

Option Pins

Configuration

Description

SPI_EN

Open

I

2

C Mode. The signal path for I

2

C communication between the MCU

and the PMIC is enabled.

Closed (Default)

SPI mode. The signal path for SPI communication between the MCU

and the PMIC is enabled.

GPIO3, SDA2/SDO

Open

GPIO mode. GPIO2 from PMIC is connected to PM7 of the MCU

through a level translator.

GPIO3,SDA2/SDO: Closed

(Default)

I

2

C Mode (J18 VIO, I2C/SPI:

Open)

Q&A Watchdog mode. GPIO3

supports the Q&A Watchdog

when PMIC is in the Alternative

function and the I

2

C mode is

selected. This setting is also

done on connector J24 by closing

GPIO2 to SCL2/CS if I2C2 is

wanted to be used.

SPI mode (J18 VIO, I2C/SPI:

Closed)

SPI mode, Chip Select. GPIO2

and GPIO3 supports SPI

communication when the PMIC

is in the Alternative function.

This setting is also done on

connector J24 by closing GPIO2

to SCL2/CS if I2C2 is wanted to

be used.

GPIO6, nERR_MCU, GPIO7

Open (Default)

GPIO mode. GPIO6 of the PMIC is connected to PP5 of the through

a level translator.

GPIO6, nERR_MCU Closed

System error count down input signal from the MCU. VIO Select

must be 3.3 V. GPIO6 or GPIO7 supports the system error count

down from the MCU when the PMIC is in the Alternative function.

nERR_MCU, GPIO7 Closed

EVM Details

SLVUC20A – MARCH 2021 – REVISED AUGUST 2022

LP876242-Q1 Evaluation Module

5

Copyright © 2022 Texas Instruments Incorporated