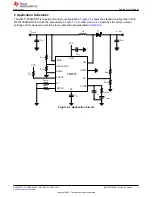

6.1 Schematic

shows the EVM schematic.

PGND

PGND

VOUT

VIN

TP2

SW

TP3

VOUT+

10uF

C9

0

R3

J1

J4

J5

J2

2200pF

C1

10uF

C6

1000pF

C3

100nF

C4

10nF

C5

1uH

L1

TP4

VIN-

TP1

VIN+

TP5

GND

J3

VIN = 3V- 9VDC

VOUT = 12VDC

Fsw = 2.1MHz

0

R1

100nF

C19

1

µ

F

C21

VCC

PGND

VIN

0

R4

PGND

AGND

BIAS

100pF

C24

VCC

AGND

BIAS-IC

PGOOD

COMP

SS

SYNC

BIAS-IC

COMP

SS

SYNC

VOUT

VIN

BIAS

60V

D2

60V

D3

INPUT VOLTAGE SELECTION

UVLO Shutdown

VCC

VAUX

TP7

VAUX

TP11

SD

1

2

3

J6

1

2

J8

1

2

3

J7

1

2

J9

10.0k

R17

Q1

BSS123

UVLO

Default: OPEN

Default: Pins 2-3

10.0

R7

VOUT

AGND

3V

D4

Diode clamp FB

TP8

VOUT+

TP10

VOUT-

MODE

100nF

C22

10uF

C7

10uF

C8

100nF

C20

2.00

R2

10uF

C10

4.53k

R13

49.9k

R8

NC

15

PGND

16

PGND

1

VCC

2

BIAS

3

PGOOD

4

RT

5

EN/UVLO/SYNC

6

AGND

7

SS

10

COMP

8

FB

9

MODE

11

SW

12

SW

13

SW

14

EP

17

LM5157QRTERQ1

U1

VCC

VAUX

PGOOD

100k

R10

100k

R11

PGND

AGND

NT1

Net-Tie

1

3

2

45V

D1

AGND

AGND

1nF

C23

FB

FB

1.6A/0.8A

4.7uF

C13

4.7uF

C14

4.7uF

C15

4.7uF

C16

4.7uF

C17

4.7uF

C18

100pF

C27

22nF

C25

9.53k

R14

71.5k

R12

61.9k

R5

1.6A/0.8A

LM5157EVM-BST

2.61k

R19

10nF

C26

100uF

C11

100uF

C12

1.5uH

L2

MODE

AGND

0

R15

37.4k

R16

62.0k

R18

100k

R20

1

2

3

4

5

6

7

8

J11

0

R9

MODE Select

AGND

UVLO

TP9

UVLO

5

4

1

2

3

6

7

J10

TP12

AGND

TP6

SYNC

22uF

C2

Default: Pins 3-4

4.99

R6

Default: OPEN

Default: OPEN

Copyright © 2021, Texas Instruments Incorporated

Figure 6-7. LM5157EVM-BST Schematic

Design Files

SNVU739A – OCTOBER 2020 – REVISED AUGUST 2021

LM5157EVM-BST Evaluation Module

15

Copyright © 2021 Texas Instruments Incorporated