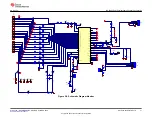

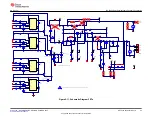

CHG

DSG

FUSEPIN

FUSE

VSS

PGND

VSS

Red

D3

FUSE

10k

R57

10M

R51

10M

R43

10M

R50

5.1k

R59

5.1k

R82

20k

R66

100

R67

20k

R79

1

10M

R42

1

2

3

F1

SFK-3030

DNP

BQ771807DPJR

VDD

1

V5

2

V4

3

V3

4

V2

5

V1

6

VSS

7

OUT

8

PAD

9

U4

BQ771807DPJR

VDD

1

V5

2

V4

3

V3

4

V2

5

V1

6

VSS

7

OUT

8

PAD

9

U5

1.0k

R78

1.0k

R69

5.1k

R61

5.1k

R62

5.1k

R64

16V

D4

10M

R35

DNP

FBAT

TP25

TP26

TP27

TP28

TP23

TP22

TP34

TP33

TP20

0

R46

DNP

0

R56

51

R55

DNP

40V

D13

16V

D6

16V

D5

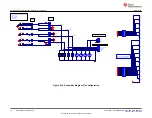

7P

6P

5P

4P

3P

2P

1P

100

R81

1.0k

R75

1.0k

R72

TP30

TP31

TP29

TP24

TP21

TP32

TP35

100V

D7

PACK-

PACK+

PGND

PACK-

PACK+

E2

PGND

1

2

J8

DNP

E1

CPACK+

CPACK+

PACK

LD

DSG

PDSG

PCHG

CHG

FUSE

PCHG

PDSG

PACK

LD

Output

6A max

D3, R45, and R48 are not required in design, but used to simulate fuse blown condition.

1

CD

NT2

Net-Tie

CPACK+

PACK+

TP36

PGND

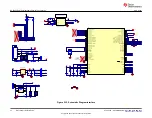

BQ771807DPJR

VDD

1

V5

2

V4

3

V3

4

V2

5

V1

6

VSS

7

OUT

8

PAD

9

U3

BQ771807DPJR

VDD

1

V5

2

V4

3

V3

4

V2

5

V1

6

VSS

7

OUT

8

PAD

9

U2

8P

1.0k

R86

1.0k

R83

1.0k

R85

1.0k

R84

1.0k

R54

1.0k

R47

1.0k

R53

1.0k

R49

1.0k

R37

1.0k

R32

1.0k

R36

1.0k

R34

11P

10P

9P

12P

15P

14P

13P

16P

100

R41

100

R31

20k

R58

20k

R38

4

7,8

1,2,3

5,6,

Q7

DNP

4

7,8

1,2,3

5,6,

Q8

4

7,8

1,2,3

5,6,

Q9

10M

R52

BAT+

13V-27V (2-4 cells + VOUT)

13V-47V (2-8 cells + VOUT)

13V-67V (2-12 cells + VOUT)

7.5k

R45

4

7

,8

1

,2

,3

5

,6

,

Q12

SI7898DP-E3

4

7,8

1,2,3

5,6,

Q3

DNP

0.1uF

C32

0.1uF

C29

DNP

0.1uF

C30

DNP

0.1uF

C37

0.1uF

C38

0.1uF

C34

DNP

0.1uF

C36

DNP

0.1uF

C42

0.1uF

C45

Desired voltage to Q11 Gate: <12V, >5V

0.1uF

C41

0.1uF

C49

0.1uF

C54

0.1uF

C47

0.1uF

C31

0.1uF

C33

0.1uF

C35

0.1uF

C39

0.1uF

C40

0.1uF

C43

0.1uF

C44

0.1uF

C46

0.1uF

C48

0.1uF

C50

0.1uF

C51

0.1uF

C52

0.1uF

C53

0.1uF

C55

0.1uF

C56

0.1uF

C57

4.7k

R40

4.7k

R39

Q10

3

1

2

Q13

3

1

2

Q11

3

1

2

Q4

27k

R80

62k

R60

95.3k

R44

4.7k

R33

DNP

10V

D8

1

2

3

4

1

2

3

4

J9

3

1

2

Q6

3

1

2

Q2

DNP

100V

D10

DNP

100V

D11

DNP

100V

D12

DNP

VSS

100V

D9

5.1k

R68

5.1k

R73

5.1k

R76

5.1k

R70

DNP

5.1k

R71

DNP

5.1k

R74

5.1k

R77

3

1

2

Q5

5.1k

R63

7.5k

R48

7.5k

R65

Figure 5-11. Schematic Diagram FETs

BQ76952EVM Circuit Module Physical Construction

SLUUC33A – NOVEMBER 2019 – REVISED OCTOBER 2020

BQ76952 Evaluation Module

43

Copyright © 2020 Texas Instruments Incorporated