STA309A

I

2

C bus operation

Doc ID 13855 Rev 4

17/67

address and if a match is found, it acknowledges the identification on SDA bus during the

9

th

-bit time. The byte following the device identification byte is the internal space address.

5.3 Write

operation

Following the START condition the master sends a device select code with the RW bit set

to 0. The STA309A acknowledges this and the writes for the byte of internal address.

After receiving the internal byte address the STA309A again responds with an

acknowledgement.

5.3.1 Byte

write

In the byte write mode the master sends one data byte, this is acknowledged by the Omega

DDX core. The master then terminates the transfer by generating a STOP condition.

5.3.2 Multi-byte

write

The multi-byte write modes can start from any internal address. The master generating a

STOP condition terminates the transfer.

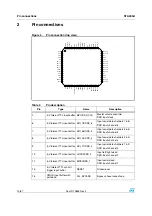

Figure 4.

Write mode sequence

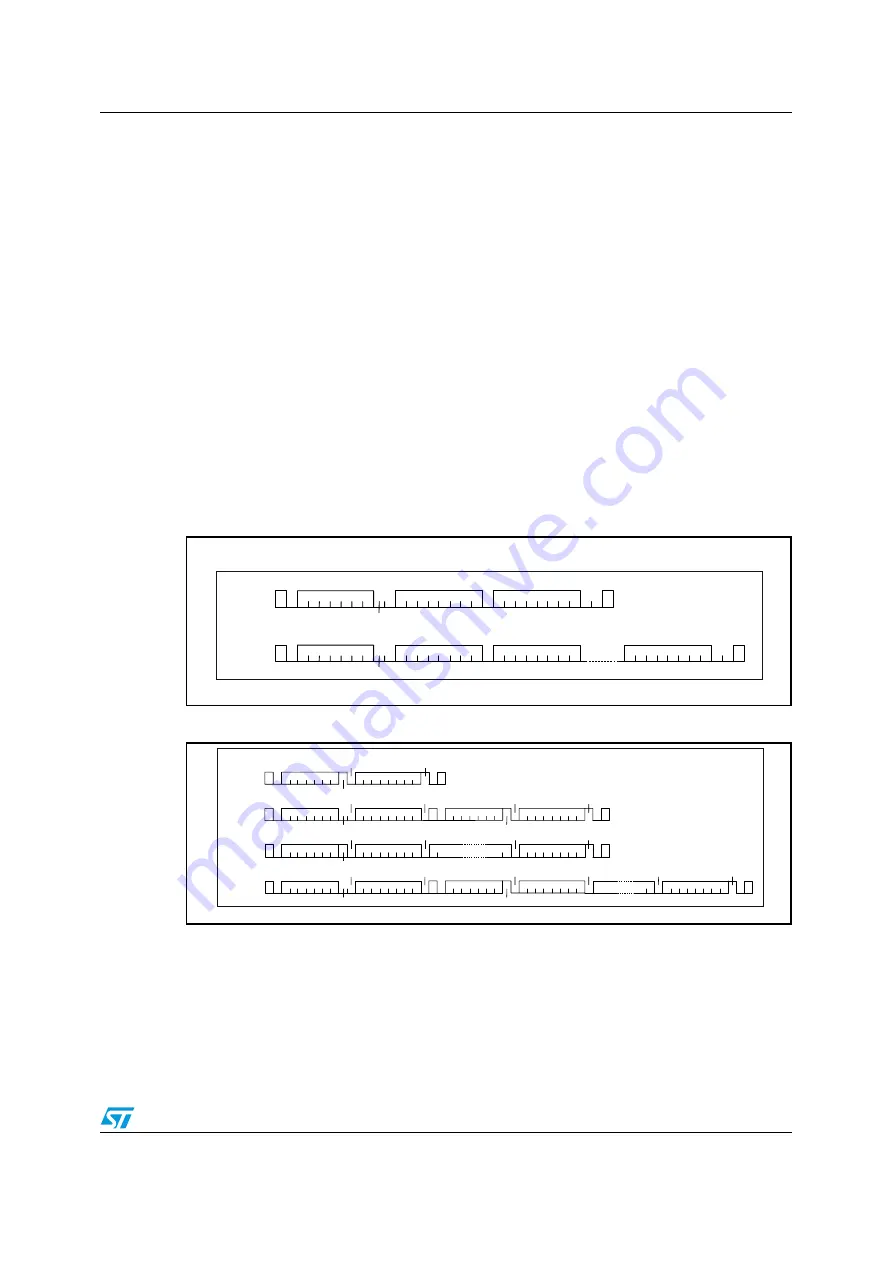

Figure 5.

Read mode sequence

DEV-ADDR

ACK

START

RW

SUB-ADDR

ACK

DATA IN

ACK

STOP

BYTE

WRITE

DEV-ADDR

ACK

START

RW

SUB-ADDR

ACK

DATA IN

ACK

STOP

MULTIBYTE

WRITE

DATA IN

ACK

DEV-ADDR

ACK

START

RW

DATA

NO ACK

STOP

CURRENT

ADDRESS

READ

DEV-ADDR

ACK

START

RW

SUB-ADDR

ACK

DEV-ADDR

ACK

STOP

RANDOM

ADDRESS

READ

DATA

NO ACK

START

RW

DEV-ADDR

ACK

START

DATA

ACK

DATA

ACK

STOP

SEQUENTIAL

CURRENT

READ

DATA

NO ACK

DEV-ADDR

ACK

START

RW

SUB-ADDR

ACK

DEV-ADDR

ACK

SEQUENTIAL

RANDOM

READ

DATA

ACK

START

RW

DATA

ACK

NO ACK

STOP

DATA

RW=

HIGH