1-25

IC

VGN-

S36C/S36GP/S36LP/S36SP/S36TP/S38CP/

S52B/

S62PS/S62PSY/S62S/

S350F/S350FP/

S360/S360P/

S370F

(J/AM

/AO

)

Confidential

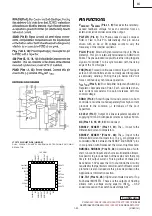

M93C46-WDW6T (ST MICROELECTRONICS)

SERIAL MICROWIRE BUS EEPROM 1Kbit

– TOP VIEW –

M93C06/46/56/66 - W

Warning: DU = Don't Use

Table 1. Signal Names

Figure 1. Logic Diagram

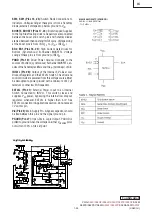

MAXTG069 (MAXIM)

LOW-COST MULTICHEMISTRY BATTERY CHARGER

28

27

26

25

24

23

22

IINP

CSSP

CSSN

DHI

BST

LX

DLOV

8

9

10

11

12

13

14

SHDN

ICHG

ACIN

ACOK

REFIN

ICTL

GND

15

16

17

18

19

20

21

VCTL

BATT

CELLS

CSIN

CSIP

PGND

DLO

7

6

5

4

3

2

1

CCV

CCI

CCS

REF

CLS

LDO

DCIN

MAX1908

THIN QFN

TOP VIEW

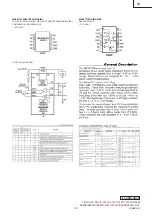

ELECTRICAL CHARACTERISTICS

(VDCIN = VCSSP = VCSSN = 18V, VBATT = VCSIP = VCSIN = 12V, VREFIN = 3V, VVCTL = VICTL = 0.75 x VREFIN, CELLS = float, CLS =

REF, VBST - VLX = 4.5V, ACIN = GND = PGND = 0, CLDO = 1µF, LDO = DLOV, CREF = 1µF; CCI, CCS, and CCV are compensated

per Figure 1a;

TA = 0°C to +85°C

, unless otherwise noted. Typical values are at TA = +25°C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

CHARGE VOLTAGE REGULATION

VVCTL = VREFIN (2, 3, or 4 cells)

-0.5

+0.5

VVCTL = VREFIN/20 (2, 3, or 4 cells)

-0.5

+0.5

Battery Regulation Voltage

Accuracy

VVCTL = VLDO (2, 3, or 4 cells)

-0.5

+0.5

%

VCTL Default Threshold

VVCTL rising

4.0

4.1

4.2

V

REFIN Range

(Note 1)

2.5

3.6

V

REFIN Undervoltage Lockout

VREFIN falling

1.20

1.92

V

CHARGE CURRENT REGULATION

CSIP to CSIN Full-Scale Current-

Sense Voltage

VICTL = VREFIN

71.25

75

78.75

mV

VICTL = VREFIN

-6

+6

VICTL = VREFIN x 0.6

-5

+5

Charging Current Accuracy

VICTL = VLDO

-6

+6

%

ICTL Default Threshold

VICTL rising

4.0

4.1

4.2

V

BATT/CSIP/CSIN Input Voltage

Range

0

19

V

VDCIN = 0 or VICTL = 0 or

SHDN

= 0

1

CSIP/CSIN Input Current

VCSIP = VCSIN = 12V

400

650

µA

Cycle-by-Cycle Maximum Current

Limit

IMAX

RS2 = 0.015

Ω

6.0

6.8

7.5

A

ICTL Power-Down Mode

Threshold Voltage

VICTL rising

REFIN /

100

REFIN /

55

REFIN /

33

V

VVCTL = VICTL = 0 or 3V

-1

+1

ICTL, VCTL Input Bias Current

VDCIN = 0, VVCTL = VICTL= VREFIN = 5V

-1

+1

µA

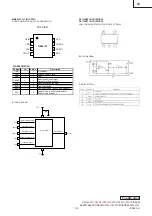

ELECTRICAL CHARACTERISTICS (continued)

(V

DCIN

= V

CSSP

= V

CSSN

= 18V, V

BATT

= V

CSIP

= V

CSIN

= 12V, V

REFIN

= 3V, V

VCTL

= V

ICTL

= 0.75 x V

REFIN

, CELLS = float, CLS =

REF, V

BST

- V

LX

= 4.5V, ACIN = GND = PGND = 0, C

LDO

= 1µF, LDO = DLOV, C

REF

= 1µF; CCI, CCS, and CCV are compensated

per Figure 1a;

T

A

= 0°C to +85°C

, unless otherwise noted. Typical values are at T

A

= +25°C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

VDCIN = 5V, VREFIN = 3V

-1

+1

REFIN Input Bias Current

VREFIN = 5V

-1

+1

µA

ICHG Transconductance

GICHG

VCSIP - VCSIN = 45mV

2.7

3

3.3

µA/mV

VCSIP - VCSIN = 75mV

-6

+6

VCSIP - VCSIN = 45mV

-5

+5

ICHG Accuracy

VCSIP - VCSIN = 5mV

-40

+40

%

ICHG Output Current

VCSIP - VCSIN = 150mV, VICHG = 0

350

µA

ICHG Output Voltage

VCSIP - VCSIN = 150mV, ICHG = float

3.5

V

INPUT CURRENT REGULATION

CSSP-to-CSSN Full-Scale

Current-Sense Voltage

71.25

75

78.75

mV

VCLS = VREF

-4

+4

Input Current-Limit Accuracy

VCLS = VREF / 2

-7.5

+7.5

%

CSSP, CSSN Input Voltage

Range

8

28

V

VDCIN = 0

0.1

1

CSSP, CSSN Input Current

VCSSP = VCSSN = VDCIN > 8V

350

600

µA

CLS Input Range

1.6

REF

V

CLS Input Bias Current

VCLS = 2V

-1

+1

µA

IINP Transconductance

GIINP

VCSSP - VCSSN = 75mV

2.7

3

3.3

µA/mV

VCSSP - VCSSN = 75mV

-5

+5

IINP Accuracy

VCSSP - VCSSN = 37.5mV

-7.5

+7.5

%

IINP Output Current

VCSSP - VCSSN = 150mV, VIINP = 0

350

µA

IINP Output Voltage

VCSSP - VCSSN = 150mV,VIINP = float

3.5

V

SUPPLY AND LDO REGULATOR

DCIN Input Voltage Range

VDCIN

8

28

V

VDCIN falling

7

7.4

DCIN Undervoltage Lockout Trip

Point

VDCIN rising

7.5

7.85

V

DCIN Quiescent Current

IDCIN

8.0V < VDCIN < 28V

3.2

6

mA

VBATT = 19V, VDCIN = 0

1

BATT Input Current

IBATT

VBATT = 2V to 19V, VDCIN = 19.3V

200

500

µA

LDO Output Voltage

8V < VDCIN < 28V, no load

5.25

5.4

5.55

V

LDO Load Regulation

0 < ILDO < 10mA

34

100

mV

LDO Undervoltage Lockout Trip

Point

VDCIN = 8V

3.20

4

5.15

V

REFERENCE

REF Output Voltage

0 < IREF < 500µA

4.072

4.096

4.120

V