Semiconductor Group

8-2

1997-10-01

Fail Safe Mechanisms

C541U

8.1.1 Input Clock Selection

The input clock rate of the watchdog timer is derived from the system clock of the C541U. There is

a prescaler available, which is software selectable and defines the input clock rate. This prescaler

is controlled by bit WDTPSEL in the SFR WDTREL. Tabel 8-1 shows resulting timeout periods at

f

OSC

= 12 MHz.

Special Function Register WDTREL (Address 86H)

Reset Value : 00H

Immediately after start, the watchdog timer is initialized to the reload value programmed to

WDTREL.0-WDTREL.6. After an external hardware reset, an oscillator watchdog power on reset,

or a watchdog timer reset, register WDTREL is cleared to 00H. The lower seven bits of WDTREL

can be loaded by software at any time.

Bit

Function

WDTPSEL

Watchdog timer prescaler select bit.

If WDTPSEL=0, the watchdog timer is clocked by

f

OSC

/12 (default after

reset).

If WDTPSEL=1, the watchdog timer is clocked by

f

OSC

/192

WDTREL.6 - 0

Seven bit reload value

for the high-byte of the watchdog timer. This value is loaded to WDTH

when a refresh is triggered by a consecutive setting of bits WDT and

SWDT.

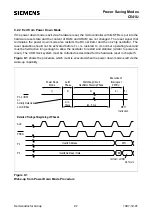

Table 8-1

Watchdog Timer Time-Out Periods (WDTPSEL = 0)

WDTREL

Time-Out Period

f

OSC

= 12 MHz

Comments

00H

32.768 ms

This is the default value

80H

0.55 s

Maximum time period

7FH

256

µ

s

Minimum time period

MSB

LSB

Bit No.

WDT

86H

WDTREL

7

6

5

4

3

2

1

0

Reload Value

PSEL

Содержание C541U

Страница 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Страница 7: ......

Страница 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Страница 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

Страница 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Страница 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Страница 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...

Страница 192: ...Semiconductor Group 12 7 Index C541U ...