FO-4400U

FO-CS1

5 – 4

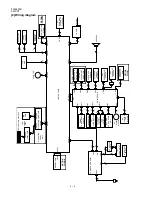

PIN

I/O

Name

Function

101

I/I/O

IOIS16-/PTD[5]

IOIS16(PCMCIA)/input port D

102

O

BACK-

Bus acknowledge

103

I

BREQ-

Bus request

104

i

WAIT-

Hardware wait request

105

O/I/O

DACK0/PTE[0]

DMA acknowledge 0/input/output port E

106

O/I/O

DACK1/PTE[1]

DMA acknowledge 1/input/output port E

107

O/I/O

DRAK0/PTE[2]

DMA request acknowledge/input/output port E

108

O/I/O

DRAK1/PTE[3]

DMA request acknowledge/input/output port E

109

I/O

AUDATA[0]/PTF[0] AUD data/ input/output port F

110

I/O

AUDATA[1]/PTF[1] AUD data/ input/output port F

111

I/O

AUDATA[2]/PTF[2] AUD data/ input/output port F

112

I/O

AUDATA[3]/PTF[3] AUD data/ input/output port F

113

O/I/O

AUDSYNC-/PTF[4] AUD synchronous/ input/output port F

114

I

TDI/PTG[0]

Data input(H-UDI)/input port G

115

—

Vss

Internal power supply (0 V)

116

I

TCK/PTG[1]

Clock(H-UDI)/input port G

117

—

Vcc

Internal power supply (1.9 V)

118

I

TMS/PTG[2]

Mode select(H-UDI)/input port G

119

I

TRST-/PTG[3]

Reset(H-UDI)/input port G

120

O/I/O

TDO/PTF[5]

Data output(H-UDI)/input/output port F

121

O/I/O

ASEBRKAK-/PTF[6] ASE break acknowledge(H-UDI)/input/output port F

122

I

ASEMD0-*

3

ASE mode(H-UDI)

123

—

Vcc-PLL1*

2

PLL1 power supply (1.9 V)

124

—

CAP1

PLL1 external capacitance pin

125

—

Vss-PLL1*

2

PLL1 power supply (0 V)

126

—

Vss-PLL2*

2

PLL2 power supply (0 V)

127

—

CAP2

PLL2 external capacitance pin

128

—

Vcc-PLL2*

2

PLL2 power supply (1.9 V)

129

I

MD1

Clock mode setting

130

—

Vss

Internal power supply (0 V)

131

O

XTAL

Clock oscillator pin

132

I

EXTAL

External clock/crystal oscillator pin

133

O/I/O

STATUS0/PTE[4]

Processor status/input/output port E

134

O/I/O

STATUS1/PTE[5]

Processor status/input/output port E

135

I/O

TCLK/PTE[6]

TMU or RTC clock input/output/input/output port E

136

O/I/O

IRQOUT-/PTE[7]

Interrupt request notification/output/input/output port E

137

—

VssQ

Input/output power supply (0 V)

138

I/O

CKIO

System clock input/output

HD6417706F133 (IC24) Terminal description (2/2)

PIN

I/O

Name

Function

139

—

VccQ

Input/output power supply (3.3 V)

140

O

TxD0/SCPT[0]

SCI transmit data 0/SC port

141

I/O

SCK0/SCPT[1]

SCI clock 0/SC port

142

O

TxD2/SCPT[2]

SCIF transmit data 2/SC port

143

I/O

SCK2/SCP[3]

SCIF clock 2/SC port

144

O/I/O

RTS2-/SCPT[4]

SCIF transmit request 2/SC port

145

I

RxD0/SCPT[0]

SCI receive data 0/SC port

146

I

RxD2/SCPT[2]

SCIF receive data 2/SC port

147

I

CTS2-/IRQ5/SCPT[5]

SCIF transmit clear/external interruption request/SC port

148

—

Vss

Internal power supply (0 V)

149

I

RESETM-

Manual reset request

150

—

Vcc

Internal power supply (1.9 V)

151

I/I/I/O

IRQ0/IRL0-/PTH[0] External interrupt request/input/output port H

152

I/I/I/O

IRQ1/IRL1-/PTH[1] External interrupt request/input/output port H

153

I/I/I/O

IRQ2/IRL2-/PTH[2] External interrupt request/input/output port H

154

I/I/I/O

IRQ3/IRL3-/PTH[3] External interrupt request/input/output port H

155

I/I/O

IRQ4/PTH[4]

External interrupt request/input/output port H

156

—

VssQ

Input/output power supply (0 V)

157

I

NMI

Nonmaskable interrupt request

158

—

VccQ

Input/output power supply (3.3 V)

159

I

AUDCK/PTG[4]

AUD clock/input port G

160

I/I/O

DREQ0-/PTH[5]

DMA request/input/output port H

161

I/I/O

DREQ1-/PTH[6]

DMA request/input/output port H

162

I

ADTRG-/PTG[5]

Analog trigger/input port G

163

I

MD0

Clock mode setting

164

I

MD2

Clock mode setting

165

I

RESETP-

Power-on reset request

166

I

CA

Chip activate/hardware standby request

167

I

MD3

Area 0 bus width setting

168

I

MD4

Area 0 bus width setting

169

I

MD5

Endian setting

170

—

AVss

Analog power supply (0 V)

171

I

AN[0]/PTJ[0]

A/D converter input/input port J

172

I

AN[1]/PTJ[1]

A/D converter input/input port J

173

I/O/I

AN2[2]/DA[1]/PTJ[2] A/D converter input/ D/A converter output/ input port J

174

I/O/I

AN3[3]/DA[0]/PTJ[3] A/D converter input/ D/A converter output/ input port J

175

—

AVcc

Analog power supply (3.3 V)

176

—

AVss

Analog power supply (0 V)

Notes: *1 Must be connected to the power supply even when the RTC is not used.

*2 Must be connected to the power supply even when the on-chip PLL circuits are not used.(EXcept in hardware standby mode.)

*3 Must be high level when the user system is used independently without using the emulator or H-UDI.

1. Except in hardware standby mode, all Vcc/Vss pins must be connected to the system power supply. (Supply power constantly.) In hardware

standby mode, power must be supplied at least to Vcc-RTC and Vss-RTC. If power is not supplied to Vcc and Vss pins other than Vcc-RTC

and Vss-RTC, hold the CA pin low.

2. A1, A2, A3, A7, A12, B1, C4, C7, D1, D2, D4, D7, D14, D15, E1, E2, E3, E4, F14, F17, G17, H14, H15, K14, P14, R10, T13, T15, T16, U11,

U15, and U16 must be connected to Vss.

Содержание FO 4400 - B/W Laser - All-in-One

Страница 125: ...FO 4400U FO CS1 Control PWB parts layout Top side 6 16 ...

Страница 126: ...FO 4400U FO CS1 Control PWB parts layout Bottom side 6 17 ...

Страница 128: ...FO 4400U FO CS1 LIU PWB parts layout Top side 6 19 ...

Страница 129: ...FO 4400U FO CS1 LIU PWB parts layout Bottom side 6 20 ...

Страница 132: ...FO 4400U FO CS1 Printer PWB parts layout Top side 6 23 ...

Страница 133: ...FO 4400U FO CS1 Printer PWB parts layout Bottom side 6 24 ...

Страница 135: ...FO 4400U FO CS1 Power Supply PWB parts layout 6 26 The Power supply PWB of this model employs lead free solder ...

Страница 143: ...FO 4400U FO CS1 M E M O 6 34 ...