RTC – 4553AC

Page - 4

MQ - 342 - 01

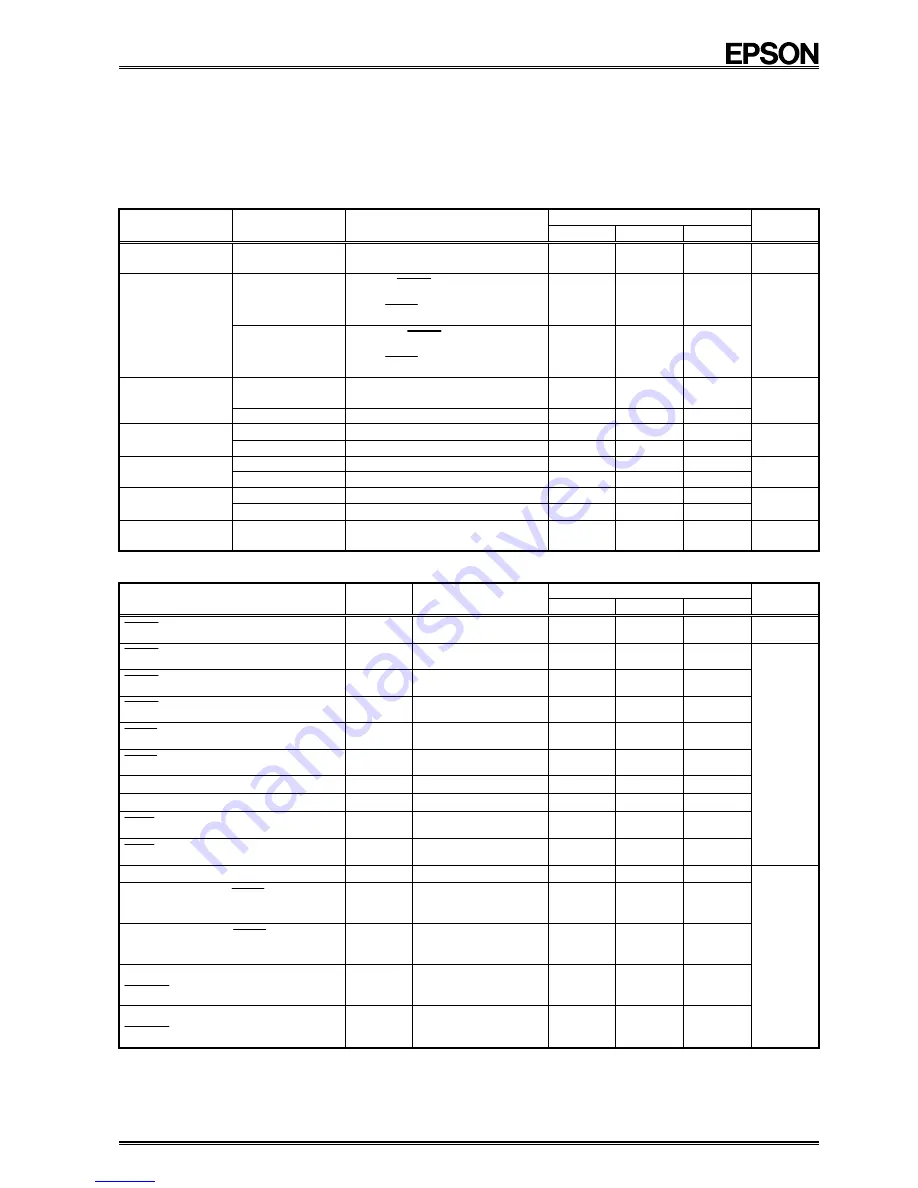

7. Electrical characteristics

7.1. DC, AC Characteristics

7.1.1. V

DD

= 5 V

(1) DC Characteristics

( GND=0 V , Ta =

−

30

°

C

∼

+70

°

C )

V

DD

= 5 V ± 10 %

Item Symbol

Condition

Min. Typ. Max.

Unit

Data retention

voltage

V

DH

—

2.0 — 5.5 V

I

DD

1

(normal operation)

SCK = 500 kHz

CS0 = L, CS1 = H

— — 100

Current

consumption

I

DD

2

(backup

operation)

SCK = 0 Hz

CS0 = H, CS1 = L

— 1.0 3.0

µ

A

V

OH

I

OH

=

−

400

µ

A

V

DD

−

0.4

— —

Output voltage

V

OL

I

OL

= 1.6 mA

—

—

0.4

V

I

OZH

V

OUT

= 5.5 V

−

2.0

— 2.0

Output leak

current

I

OZL

V

OUT

= 0 V

−

2.0

— 2.0

µ

A

V

IH

—

4/5

V

DD

—

—

Input voltage

V

IL

—

—

—

1/5

V

DD

V

I

IH

V

IN

= 5.5 V

−

2.0

— 2.0

Input current

I

IL

V

IN

= 0 V

−

2.0

— 2.0

µ

A

Oscillation

startup time

Ts

Ta = +25 °C

—

—

3.0

s

(2) AC Characteristics

( GND=0 V , Ta =

−

30

°

C

∼

+70

°

C )

V

DD

= 5 V ± 10 %

Item

Symbol

Condition

Min. Typ. Max.

Unit

SCK frequency

f

CLK

— —

—

500

kHz

SCK "L" time

t

WCKL

— 1.0

—

—

SCK "H" time

t

WCKH

— 1.0

—

—

SCK pause time

t

PS

— 1.0

—

—

CS0 setup time

t

SCS

— 0

—

—

CS0 hold time

t

HCS

— 0.5

—

—

S

IN

data setup time

t

SD

— 0.2

—

—

S

IN

data hold time

t

HD

— 0.2

—

—

WR setup time

t

SWR

— 1.0

—

—

WR hold time

t

HWR

— 0.5

—

—

µ

s

S

OUT

delay time

t

DS

0 CL=100

pF —

150

500

Time lag between CS0 , CS1 enable

and S

OUT

output

t

DSZ

1 CL=100

pF — — 100

Time lag between CS0 disable and

S

OUT

high Z

t

DSZ

2 CL=100

pF — — 100

Time lag between CS1 enable and

TP

OUT

output

t

DPZ

1 CL=100

pF — — 100

Time lag between CS1 disable and

TP

OUT

high Z

t

DPZ

2 CL=100

pF — — 100

ns

electronic components distributor