22/46

Application Note

BD71837MWV Platform Design Guide

© 2018 ROHM Co., Ltd.

No. 61AN002E Rev.001

May.2018

5.2.3. Power GND

Power ground for BUCK Converters (exposed pad) is the noisy ground because of the current loops indicated in the previous section.

Thus, the power ground should take an area as large as possible to keep the impedance low and reduce the swing of ground voltage

level.

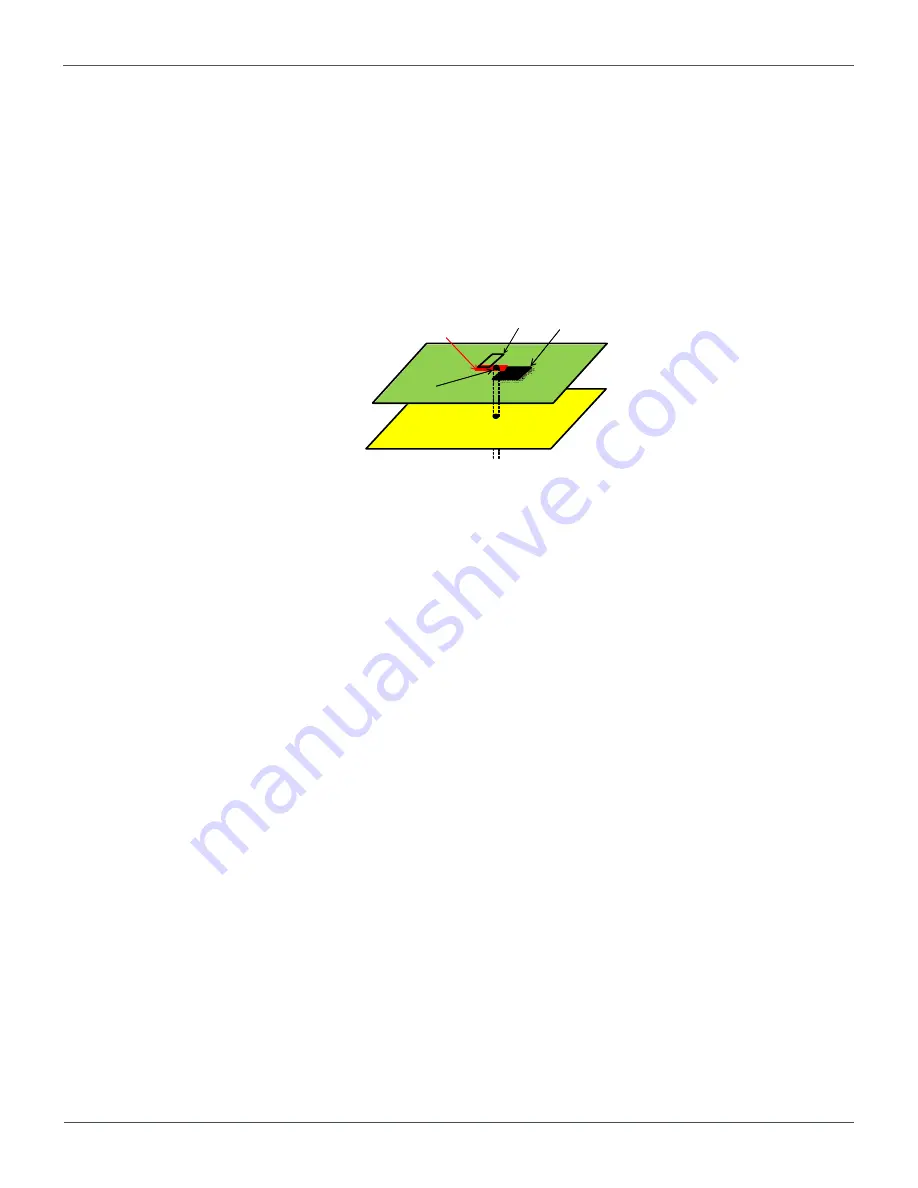

5.2.4. VSYS (Power supply for BD71837MWV analog circuit)

BUCK X_VIN (X is 1

, 2, 3… and 8) of each VR’s input should be connected to VSYS plane directly to minimize the parasitic and

common impedance effects.

The enough numbers of vias for input capacitors should be used and the decoupling capacitors should be placed as close to PMIC as

possible. The reference layout (BD71837MWV reference layout) can be referred to for your reference.

5.2.5. Other Signal Pattern Precautions

Make sure to leave adequate space between noisy lines of voltage rail and serial interface (I2C).

5.2.6. Feedback Sense Lines

Feedback sense lines (e.g., BUCK1_FB, BUCK2_FB etc.) should be routed to monitor the accurate output voltages for each voltage

rail. In order to avoid the effects of IR drop and switching noise, please make sure that the feedback sense lines are independently

routed from the point near output capacitors.

As the method for voltage sensing, “Local sensing” is recommended in all VRs.

In addition, these lines are interfered by noisy lines since these sense lines are high

impedance nodes. Please don’t route these

sense lines by overlapping with or in parallel with noisy lines such as LX, SCL and SDA.

Drastic voltage shift in feedback lines result in unexpected voltage violations.

VSYS

BD71837MWV

PTH

VSYS

(Top layer)

(Inner layer)

Input Cap

Figure 5.5 Layout for BUCK X_VIN and VSYS