222

Rockwell Automation Publication 2080-UM002N-EN-E - November 2022

Chapter 10 Use the High-Speed Counter and Programmable Limit Switch

The MH (High Preset Mask) control bit is used to enable (allow) or disable (not allow) a high

preset interrupt from occurring. If this bit is clear (0), and a High Preset Reached condition is

detected by the HSC, the HSC user interrupt is not executed.

This bit is controlled by the user program and retains its value through a power cycle. It is up

to the user program to set and clear this bit.

The ML (Low Preset Mask) control bit is used to enable (allow) or disable (not allow) a low preset

interrupt from occurring. If this bit is clear (0), and a Low Preset Reached condition is detected

by the HSC, the HSC user interrupt is not executed.

This bit is controlled by the user program and retains its value through a power cycle. It is up

to the user program to set and clear this bit.

HSC Interrupt Status

Information

The Enabled bit is used to indicate HSC interrupt enable or disable status.

The EX (User Interrupt Executing) bit is set (1) whenever the HSC sub-system begins processing

the HSC subroutine due to any of the following conditions:

• Low preset reached

• High preset reached

• Overflow condition – count up through the overflow value

• Underflow condition – count down through the underflow value

The HSC EX bit can be used in the control program as conditional logic to detect if an HSC

interrupt is executing.

The HSC sub-system will clear (0) the EX bit when the controller completes its processing of

the HSC subroutine.

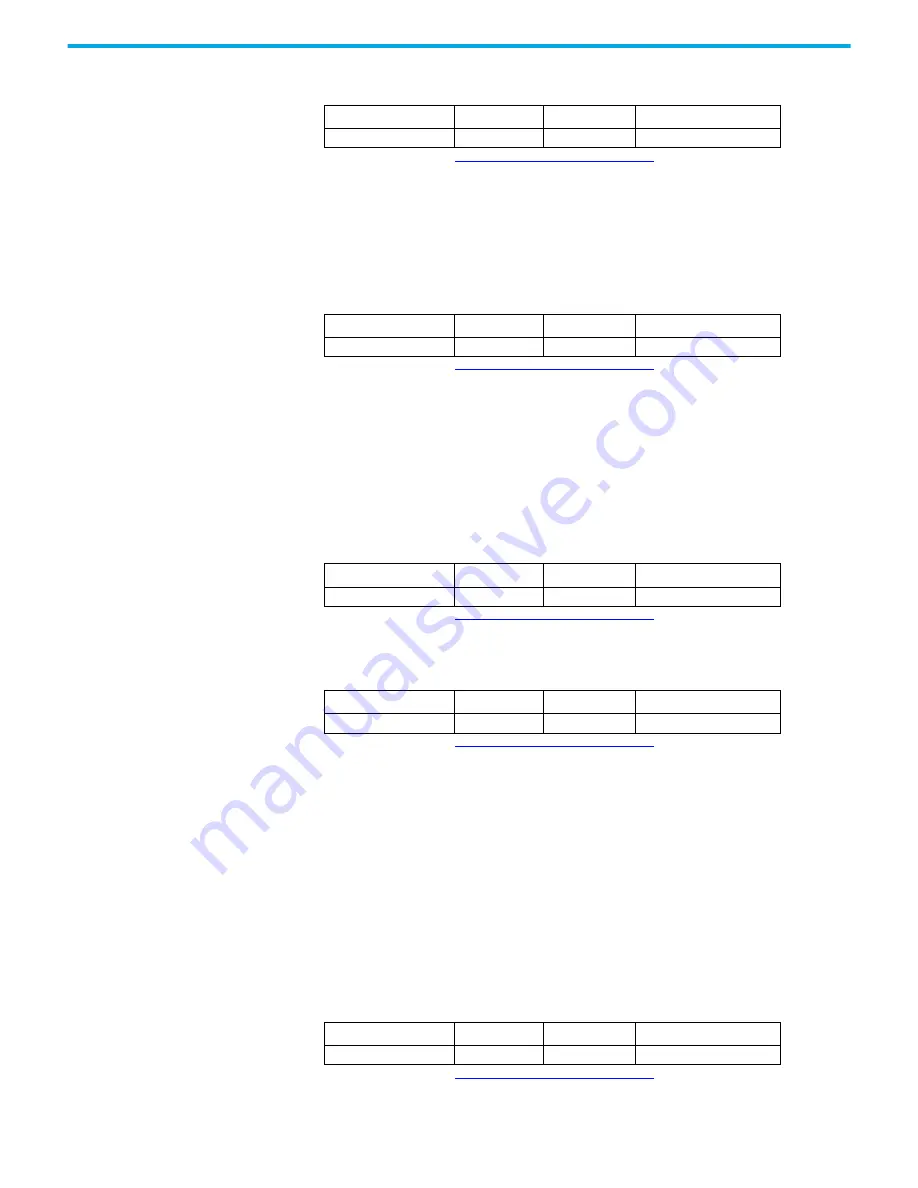

Mask for IH (HSC0.MH)

Description

Data Format

HSC Modes

(1)

(1) For Mode descriptions, see

Count Down (HSCSTS.CountDownFlag) on page 211

User Program Access

MH - High Preset Mask

bit

0…9

read only

Mask for IL (HSC0.ML)

Description

Data Format

HSC Modes

(1)

(1) For Mode descriptions, see

Count Down (HSCSTS.CountDownFlag) on page 211

User Program Access

ML - Low Preset Mask

bit

2…9

read only

User Interrupt Enable (HSC0.Enabled)

Description

Data Format

HSC Modes

(1)

(1) For Mode descriptions, see

Count Down (HSCSTS.CountDownFlag) on page 211

User Program Access

HSC0.Enabled

bit

0…9

read only

User Interrupt Executing (HSC0.EX)

Description

Data Format

HSC Modes

(1)

(1) For Mode descriptions, see

Count Down (HSCSTS.CountDownFlag) on page 211

User Program Access

HSC0.EX

bit

0…9

read only

User Interrupt Pending (HSC0.PE)

Description

Data Format

HSC Modes

(1)

(1) For Mode descriptions, see

Count Down (HSCSTS.CountDownFlag) on page 211

User Program Access

HSC0.PE

bit

0…9

read only

Содержание 2080-L50E-24AWB

Страница 14: ...14 Rockwell Automation Publication 2080 UM002N EN E November 2022 Notes ...

Страница 54: ...54 Rockwell Automation Publication 2080 UM002N EN E November 2022 Chapter 4 Wire Your Controller Notes ...

Страница 128: ...128 Rockwell Automation Publication 2080 UM002N EN E November 2022 Chapter 7 Program Execution in Micro800 Notes ...

Страница 156: ...156 Rockwell Automation Publication 2080 UM002N EN E November 2022 Chapter 8 EtherNet IP Network Notes ...

Страница 198: ...198 Rockwell Automation Publication 2080 UM002N EN E November 2022 Chapter 9 Motion Control Notes ...

Страница 232: ...232 Rockwell Automation Publication 2080 UM002N EN E November 2022 Chapter 11 Controller Security Notes ...

Страница 260: ...260 Rockwell Automation Publication 2080 UM002N EN E November 2022 Chapter 12 Using microSD Cards Notes ...

Страница 266: ...266 Rockwell Automation Publication 2080 UM002N EN E November 2022 Appendix A Modbus Mapping for Micro800 Notes ...

Страница 275: ...Rockwell Automation Publication 2080 UM002N EN E November 2022 275 Appendix B Quickstarts 10 Click Finish to complete ...

Страница 332: ...332 Rockwell Automation Publication 2080 UM002N EN E November 2022 Appendix E PID Function Blocks Notes ...

Страница 352: ...352 Rockwell Automation Publication 2080 UM002N EN E November 2022 Appendix G Connect to Networks using DF1 Notes ...

Страница 388: ...388 Rockwell Automation Publication 2080 UM002N EN E November 2022 Index Notes ...