26

Rabbit 2000/3000 Microprocessor

Description

The Carry Flag is inverted: If it is set, it becomes cleared. If it is not set, it becomes set.

Description

Compares the data in the Accumulator with the data whose address is (a) contained in word register HL, (b)

the sum of the data in index register IX plus a displacement value d, or (c) the sum of the data in index register

IY plus a displacement value d.

These compares are accomplished by subtracting the appropriate data ((HL), (IX+d), or (IY+d)) from the

Accumulator. If the value of the data in the Accumulator is less than the value of the data compared, then the

Sign Flag and the Carry Flag are set. If they are equal, the Zero Flag is set. If the data is greater than the data

in the Accumulator, then the Sign, Carry, and Zero Flags are reset. This operation does not affect the data in

the Accumulator.

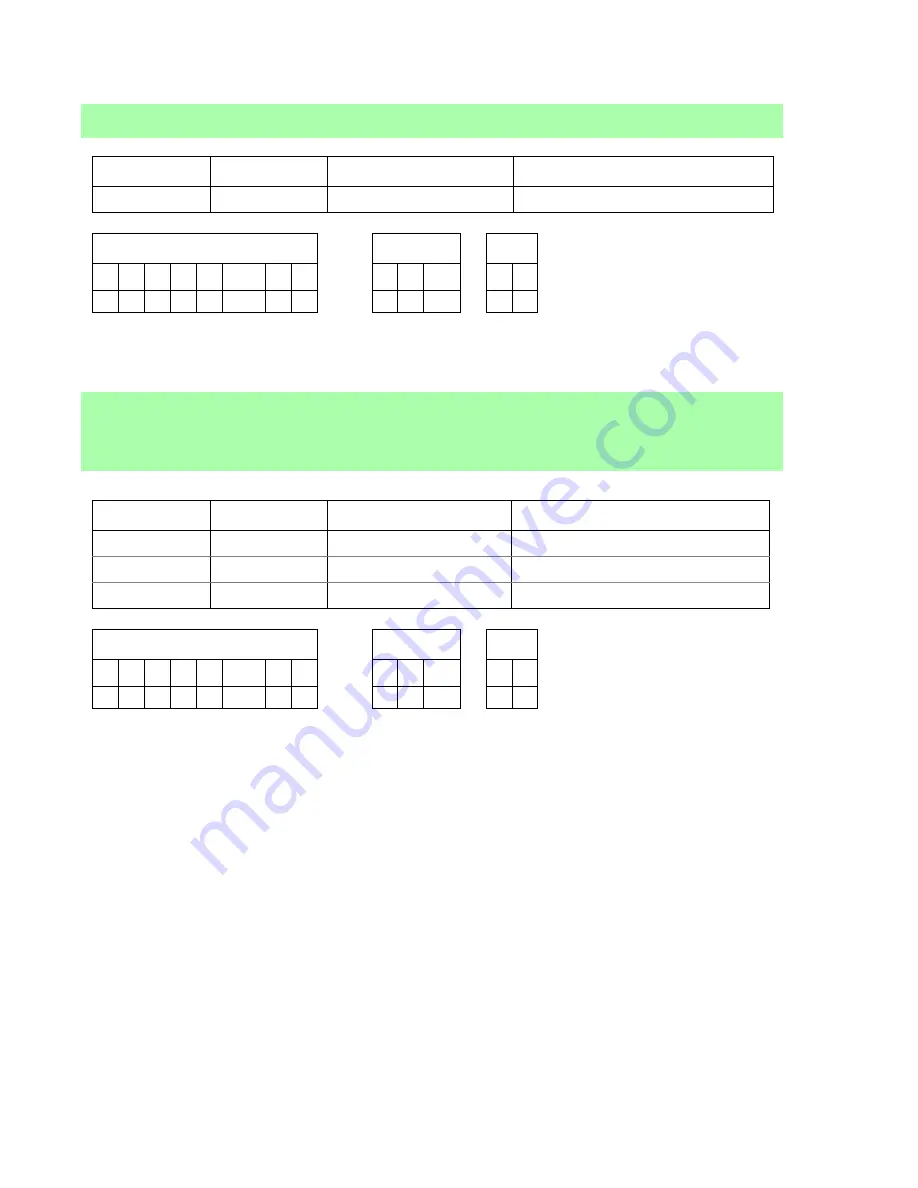

CCF

Opcode

Instruction

Clocks

Operation

3F

CCF

2

CF = ~CF

Flags

ALTD

I/O

S

Z

L/V

C

F

R

SP

S

D

-

-

-

•

•

CP (HL)

CP (IX+d)

CP (IY+d)

Opcode

Instruction

Clocks

Operation

BE

CP (HL)

5 (2,1,2)

A - (HL)

DD BE d

CP (IX + d)

9 (2,2,2,1,2)

A - (IX + d)

FE BE d

CP (IY + d)

9 (2,2,2,1,2)

A - (IY + d)

Flags

ALTD

I/O

S

Z

L/V

C

F

R

SP

S

D

•

•

V

•

•

•

Содержание 2000

Страница 2: ...ii Rabbit 2000 3000 Microprocessor...

Страница 4: ...iv Rabbit 2000 Microprocessor...

Страница 16: ...12 Rabbit 2000 3000 Microprocessor...

Страница 112: ...108 Rabbit 2000 3000 Microprocessor...

Страница 120: ...ii Rabbit 2000 3000 Microprocessor...