66

Rabbit 2000/3000 Microprocessor

Description

•

LD (SP+n),HL:

Loads the data in the L into the memory location whose address is the sum

of the data in SP and the displacement n. Then loads the data in the H into the memory location

whose address is the sum of the data in SP, the displacement n, and 1.

•

LD (SP+n),IX:

Loads the low order byte of the data in IX into the memory location whose

address is the sum of the data in SP and the displacement n. Then loads the high order byte of the

data in IX into the memory location whose address is the sum of data in SP, the displacement n,

and 1.

•

LD (SP+n),IY:

Loads the low order byte of the data in IY into the memory location whose

address is the sum of the data in SP and the displacement n. Then loads the high order byte of the

data in IY into the memory location whose address is the sum of data in SP, the displacement n,

and 1.

LD (SP+

n

),HL

LD (SP+

n

),IX

LD (SP+

n

),IY

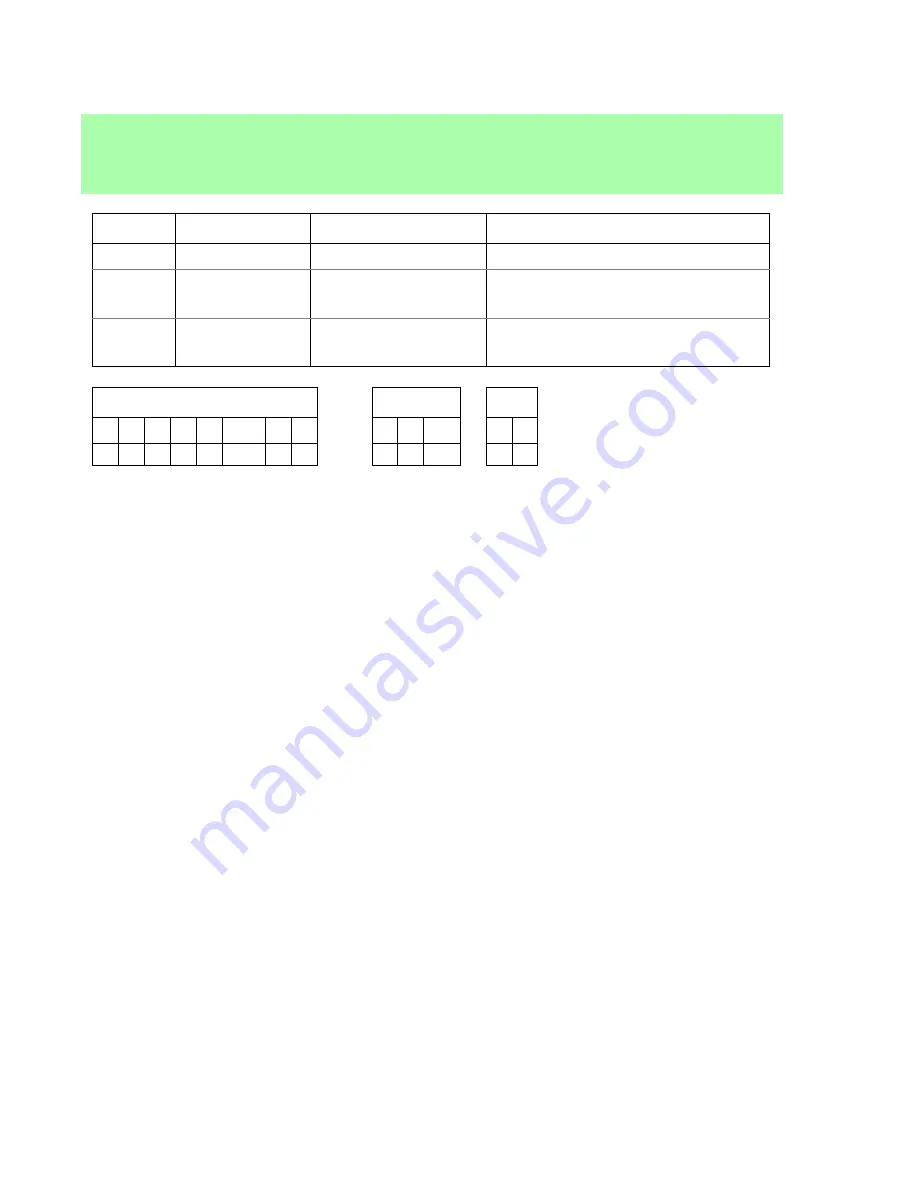

Opcode

Instruction

Clocks

Operation

D4

n

LD (SP+

n

),HL

11 (2,2,1,3,3)

(SP +

n

) = L; (SP +

n

+ 1) = H

DD D4

n

LD (SP+

n

),IX

13 (2,2,2,1,3,3)

(SP +

n

) = IX

(low)

;

(SP +

n

+ 1) = IX

(high)

FD D4

n

LP (SP+

n

),IY

13 (2,2,2,1,3,3)

(SP +

n

) = IY

(low)

;

(SP +

n

+ 1) = IY

(high)

Flags

ALTD

I/O

S

Z

L/V

C

F

R

SP

S

D

-

-

-

-

Содержание 2000

Страница 2: ...ii Rabbit 2000 3000 Microprocessor...

Страница 4: ...iv Rabbit 2000 Microprocessor...

Страница 16: ...12 Rabbit 2000 3000 Microprocessor...

Страница 164: ...160 Instruction Reference Manual...

Страница 172: ...168 Rabbit 2000 3000 Microprocessor...

Страница 174: ...170 Rabbit 2000 3000 Microprocessor...