LTE-A Module Series

EM12-G Hardware Design

EM12-G_Hardware_Design 33 / 62

GND

USB3.0_TX-

USB3.0_TX+

GND

USB3.0_RX-

USB3.0_RX+

USB3.0_RX-

USB3.0_RX+

USB3.0_TX-

USB3.0_TX+

C3

C4

USB_DP

USB_DM

R1

R2

0R

0R

USB_DM

USB_DP

C1

C2

ESD Array

100nF

100nF

100nF

100nF

Module

MCU

R3

R4

NM_0R

NM_0R

Test Points

Minimize these stubs

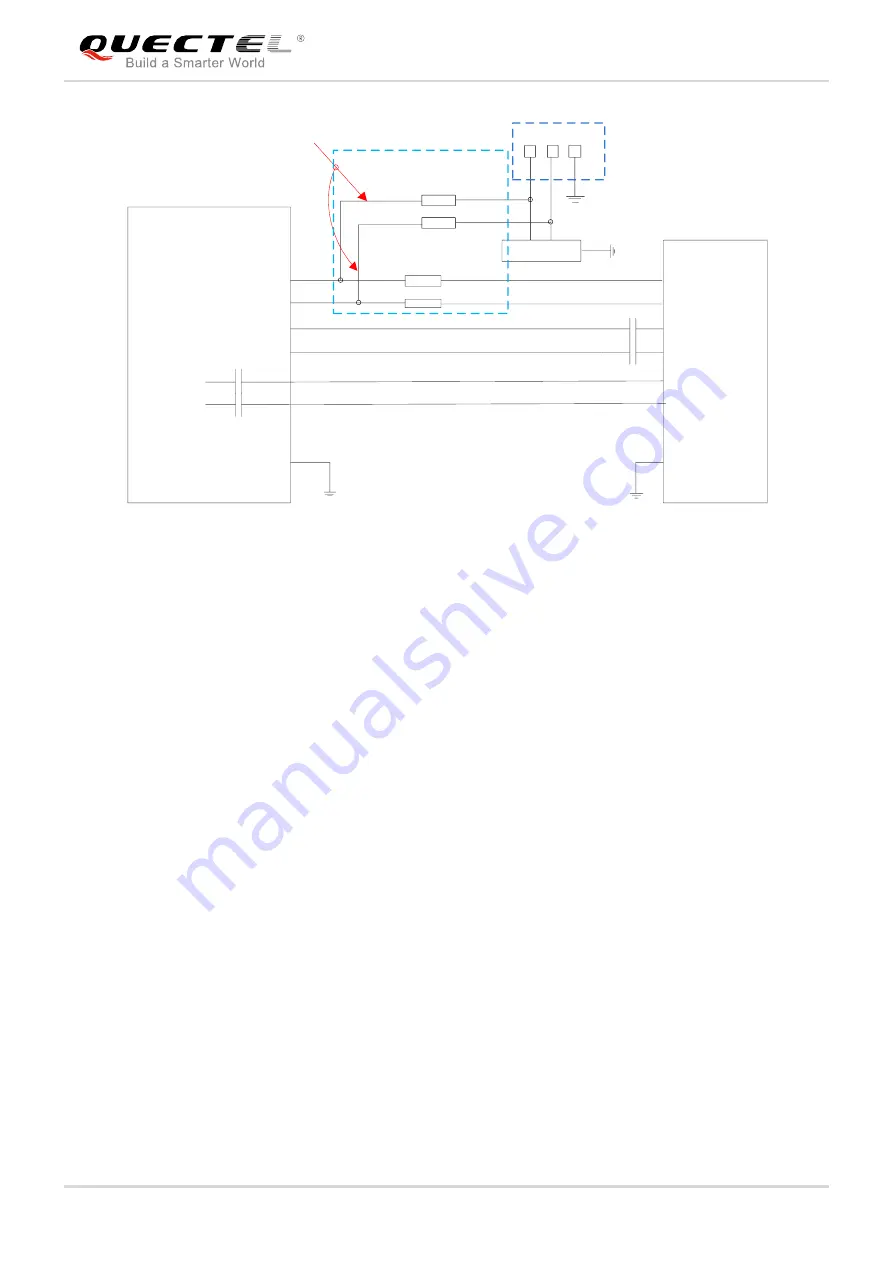

Figure 16: Reference Circuit of USB 2.0 & 3.0 Interface

In order to ensure the integrity of USB 2.0 & 3.0 data line signal, R1/R2/R3/R4 components must be

placed close to the module, capacitors C1 and C2 have been placed inside the module, capacitors C3

and C4 must be placed close to the MCU, and these components should be placed close to each other.

In order to ensure the USB interface design corresponding with USB 2.0 & 3.0 specifications, please

comply with the following principles:

It is important to route the USB 2.0 & 3.0 signal traces as differential pairs with total grounding.

1) For USB 2.0 routing traces, the trace impedance of the

differential pair should be 90Ω, and the

trace length difference between the differential pair should be less than 2mm.

2)

For USB 3.0 routing traces, the trace impedance of Tx and Rx differential pairs should be 90Ω,

and the trace length difference between Tx and Rx differential pairs should be less than

0.7mm.

Do not route signal traces under crystals, oscillators, magnetic devices or RF signal traces. It is

important to route the USB 2.0 & 3.0 differential traces in inner-layer with ground shielding on not

only upper and lower layers but also right and left sides.

If USB connector is used, please keep the ESD protection components as close as possible to the

USB connector. Pay attention to the influence of junction capacitance of ESD protection components

on USB 2.0 & 3.0 data lines. The capacitance value of ESD protection components should be less

than 2.0pF for USB 2.0, and less than 0.4pF for USB 3.0.

If possible, reserve a 0R resistor on USB_DP and USB_DM lines, respectively.