LTE Standard Module Series

EG25-GL_Hardware_Design 44 / 96

921600 bps baud rates, and the default is 115200 bps. It also supports RTS and CTS hardware flow

control, and can be used for data transmission and AT command communication.

⚫

The debug UART interface supports 115200 bps baud rate. It is used for Linux console and log

output.

The following tables show the pin definition of the UART interfaces.

Table 12: Pin Definition of Main UART Interface

Table 13: Pin Definition of Debug UART Interface

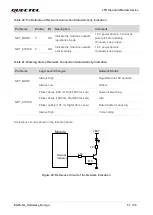

The module provides 1.8 V UART interfaces. A level translator should be used if your application is

equipped with a 3.3 V UART interface. A level translator TXS0108EPWR provided by Texas Instruments

is recommended. The following figure shows a reference design.

Pin Name

Pin No.

I/O

Description

Comment

MAIN_RI

62

DO

Main UART ring indication

1.8 V power domain.

If unused, keep it open.

MAIN_DCD

63

DO

Main UART data carrier detect

MAIN_CTS

64

DO

DTE clear to send signal from DCE

Connect to DTE

’s CTS

.

1.8 V power domain.

If unused, keep it open.

MAIN_RTS

65

DI

DTE request to send signal to DCE

Connect to DTE's RTS.

1.8 V power domain.

If unused, keep it open.

MAIN_DTR

66

DI

Main UART data terminal ready

1.8 V power domain.

Pulled up by default.

The pin can wake up the module

in the low level.

If unused, keep it open.

MAIN_TXD

67

DO

Main UART transmit

1.8 V power domain.

If unused, keep it open.

MAIN_RXD

68

DI

Main UART receive

Pin Name

Pin No.

I/O

Description

Comment

DBG_TXD

12

DO

Debug UART transmit

1.8 V power domain.

If unused, keep it open.

DBG_RXD

11

DI

Debug UART receive

Содержание EG25-GL

Страница 1: ...EG25 GL Hardware Design LTE Standard Module Series Version 1 0 0 Date 2022 09 09 Status Preliminary ...

Страница 8: ...LTE Standard Module Series EG25 GL_Hardware_Design 7 96 9 Appendix References 92 ...

Страница 10: ...LTE Standard Module Series EG25 GL_Hardware_Design 9 96 Table 42 Terms and Abbreviations 92 ...