PEX 8680 Quick Start Hardware Design Guide, Version 1.1

12

© 2011 PLX Technology, Inc. All Rights Reserved.

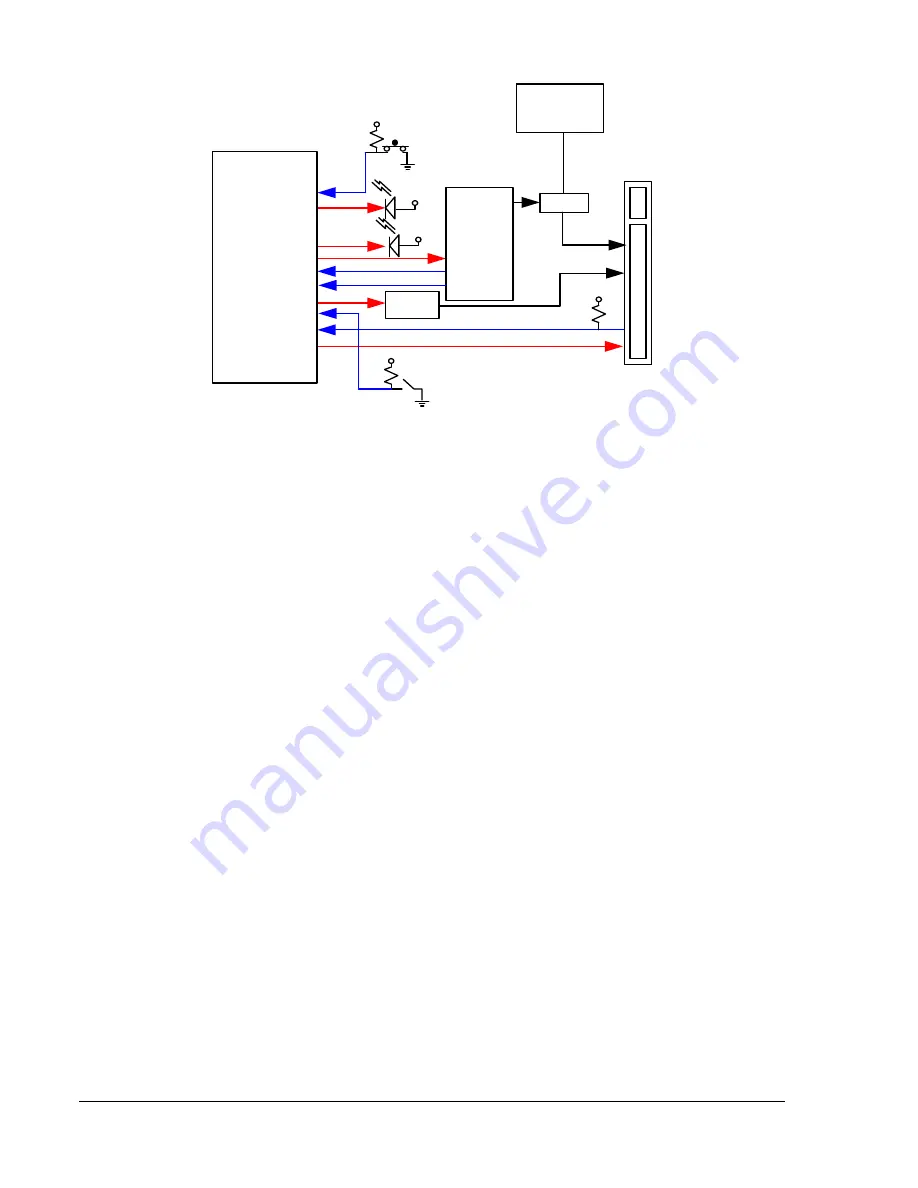

Clkenx#

Atnledx#

Pwrledx#

Pwrenx

Perstx#

VCC

System

Power

Supply

12V, 3.3V

VCC

VCC

Buttonx#

Pwrflx#

Mrlx#

Prsntx#

VCC

VCC

Hot Plug

Controller

Pwrgdx#

Clken_a#

Atnled_a#

Pwrled_a#

Pwren_a

Perst_a#

Button_a#

Pwrflt_a#

Mrl_a#

Prsnt_a#

Pwrgood_a

PEX 8680

FETs

Clock

Buffer

Figure 13. PHPC Circuit Block Diagram

When connecting the I

2

C-Port 1 to multiple I/O expander ICs, the PEX 8680 has the option of having Hot

Plug capability on eight of its downstream Ports. The PEX 8680’s I

2

C-Port 1 is the I

2

C Master, which is

designed to interface to I/O expander ICs, to build SHPCs. One 16-I/O expander connects to I

2

C-Port 1

for a single SHPC, and one 40 I/O expander connects to the I

2

C-Port 1 for two SHPCs. Both 16-I/O

expander(s) and 40-I/O expander(s) cannot concurrently connect to the I

2

C Bus. To use 40-I/O

expander(s), a register bit within the PEX 8680 must be Set, and boot with serial EEPROM is essential.

After the PEX 8680 is powered up, the state machine inside the PEX 8680 scans the number of I/O

expander ICs connecting to the I

2

C Bus, starting from Address 000h, in ascending order. If it cannot

locate the device with Address 000h, it stops the scan process. After it locates the I/O expander IC, it

automatically assigns a valid Port Number for this SHPC.

illustrates a block diagram of the

SHPC interface to the PEX 8680. The SHPC has more signals than the PHPC. Besides the 10 Hot Plug

signals mentioned at PHPC, INTERLOCK, SLOTID[3:0], and one GPIO are added to the SHPC. Also, the

interrupt signal output, INT#, from the I/O expander, should be connected to the PEX 8680’s Interrupt

Input ball, SHPC_INT#, for the PEX 8680 to service input events at the SHPC. Because the I/O

Expander requires some time to be configured upon power-up, it is recommended that GPIO[24-42]

signals from the PEX 8680 be used for slot PERST# from the I/O Expander to provide reset to

downstream slots.