NUC126

Aug. 08, 2018

Page

865

of 943

Rev 1.03

NUC12

6 S

E

RI

E

S

T

E

CH

NI

CA

L R

E

F

E

RE

NCE

MA

NUA

L

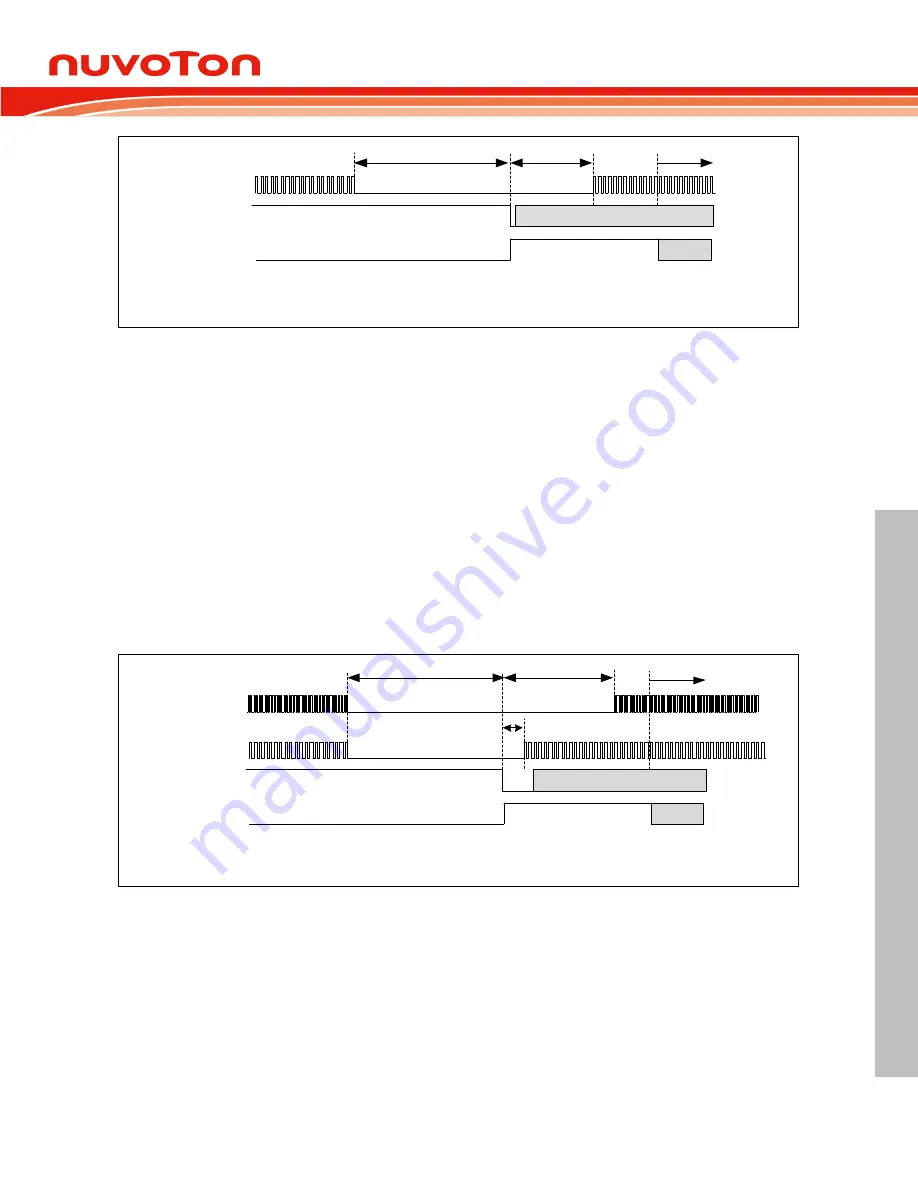

Power-down mode

HCLK

nCTS

stable count

CPU run

CTSACTLV (UART_MODEM[8]) = 1

CTSWKF

Note:

Stable count means HCLK source recovery stable count.

Figure 6.23-6 UART nCTS Wake-up Case2

Incoming Data Wake-up

When system is in Power-down mode and the WKDATEN (UART_WKCTL [1]) is set, the toggle of

incoming data (UART_RXD) pin can wake-up the system. In order to receive the incoming data after

the system wake-up, the STCOMP (UART_DWKCOMP[15:0]) shall be set. These bits field of

STCOMP indicate how many clock cycle selected by UART_CLK do the UART controller can get the

1

st

bit (start bit) when the system is wakeup from power-down mode.

When incoming data wakes system up, the incoming data will be received and stored in FIFO. If the

WKDATEN (UART_WKCTL[1]) is enabled, the toggle of incoming data (UART_RXD) pin cause the

incoming data wake-up flag DATWKF (UART_WKSTS[1]) is generated.

Note1:

The UART controller clock source should be selected as HIRC and the compensation time for

start bit is about 35us. It means that the value of STCOMP (UART_DWKCOMP[15:0]) can be set as

774.

Note2:

The

value

of

BRD(UART_BAUD[15:0])

should

be

greater

than

STCOMP

(UART_DWKCOMP[15:0]).

Power-down mode

UART_CLK

UART_RXD

DATWKF

UART_CLK stable count

CPU run

start

HCLK

stable count

Note1:

Stable count means HCLK source recovery stable count.

Note2:

UART_CLK stable count means UART clock source recovery stable count.

Figure 6.23-7 UART Data Wake-up

Received Data FIFO Reached Threshold Wake-up

The received data FIFO threshold reached wake-up function is enabled by setting WKRFRTEN

(UART_WKCTL[2]). In Power-down mode, when the number of received data in RX FIFO reaches the

threshold value RFITL (UART_FIFO[7:4]), it can wake-up the system. If the WKRFRTEN

(UART_WKCTL[2]) is enabled, the number of received data in RX FIFO reaches the threshold value

RFITL (UART_FIFO[7:4]) cause the received data FIFO reached threshold wake-up flag RFRTWKF

(UART_WKSTS[2]) is generated.

Note:

The UART controller clock source should be selected as LXT in Power-down mode to receive

data.