ISD94100 Series Technical Reference Manual

Sep 9, 2019

Page

572

of 928

Rev1.09

IS

D

9

410

0

S

ER

IE

S

T

E

C

HN

ICA

L

RE

F

E

RE

NCE

M

AN

U

AL

460800

Not recommended

BRD=0, EDIVM1 =13

BRD=24

230400

Not recommended

BRD =2, EDIVM1 =13

BRD =50

115200

Not recommended

BRD =6, EDIVM1 =13

BRD =102

57600

BRD =11

BRD =14, EDIVM1 =13

BRD =206

38400

BRD =18

BRD =22, EDIVM1 =13

BRD =311

19200

BRD =37

BRD =123, EDIVM1 =5

BRD =623

9600

BRD =76

BRD =123, EDIVM1 =10

BRD =1248

4800

BRD =154

BRD =248, EDIVM1 =10

BRD =2498

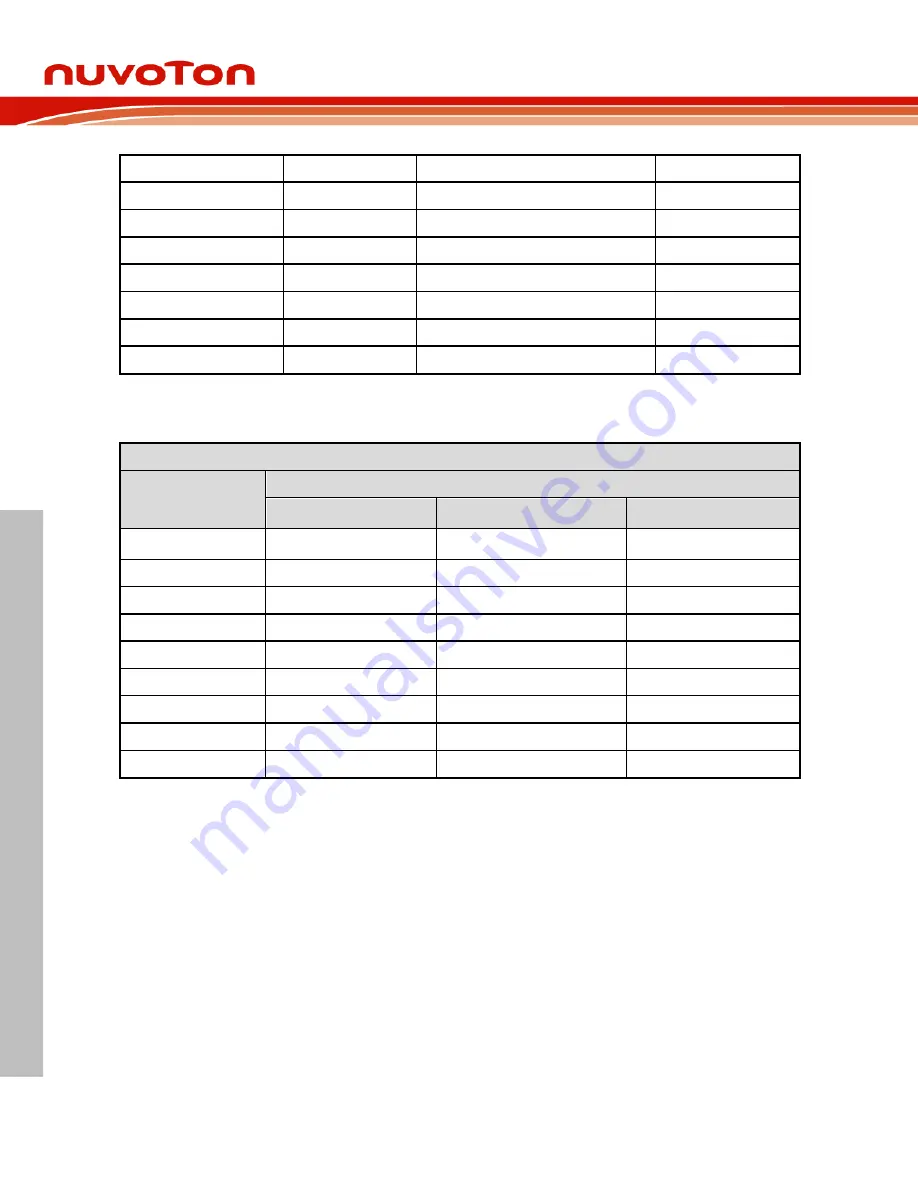

Table 6.12.5-2 UART controller Baud Rate Parameter Setting Example Table

UART Peripheral Clock = 12 MHz

Baud Rate

UART_BAUD Value

Mode 0

Mode 1

Mode 2

921600

Not support

Not recommended

0x3000_000B

460800

Not recommended

0x2D00_0000

0x3000_0018

230400

Not recommended

0x2D00_0002

0x3000_0032

115200

Not recommended

0x2D00_0006

0x3000_0066

57600

0x0000_000B

0x2D00_000E

0x3000_00CE

38400

0x0000_0012

0x2D00_0016

0x3000_0137

19200

0x0000_0025

0x2500_007B

0x3000_026F

9600

0x0000_004C

0x2A00_007B

0x3000_04E0

4800

0x0000_009A

0x2A00_00F8

0x3000_09C2

Table 6.12.5-3 UART controller Baud Rate Register Setting Example Table

6.12.5.2 UART Controller Baud Rate Compensation

The ISD94100 series UART controller supports baud rate compensation function. It is used to

optimize the precision for each bit. Two examples are given below to explain the compensation

mechanism.

-

BRCOMPDEC bit (UART_BRCOMP[31])

•

= 0: positive compensation, increase one UART clock cycle,

•

= 1: negative compensation, decrease one UART clock cycle.

-

BRCOMP bits (UART_BRCOMP[8:0]: for each bit in BRCOMP, ‘1’ means to do

compensation, while ‘0’ means not to do compensation.

Example:

(1). UART’s peripheral clock = 32.768K and baud rate is 9600

Baud rate is 9600, UART peripheral clock is 32.768K

3.413 peripheral clock/bit

Содержание ISD94100 Series

Страница 528: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 528 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 626: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 626 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 702: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 702 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...

Страница 875: ...ISD94100 Series Technical Reference Manual Sep 9 2019 Page 875 of 928 Rev1 09 ISD94100 SERIES TECHNICAL REFERENCE MANUAL...