DA70131-1/3E

III-5

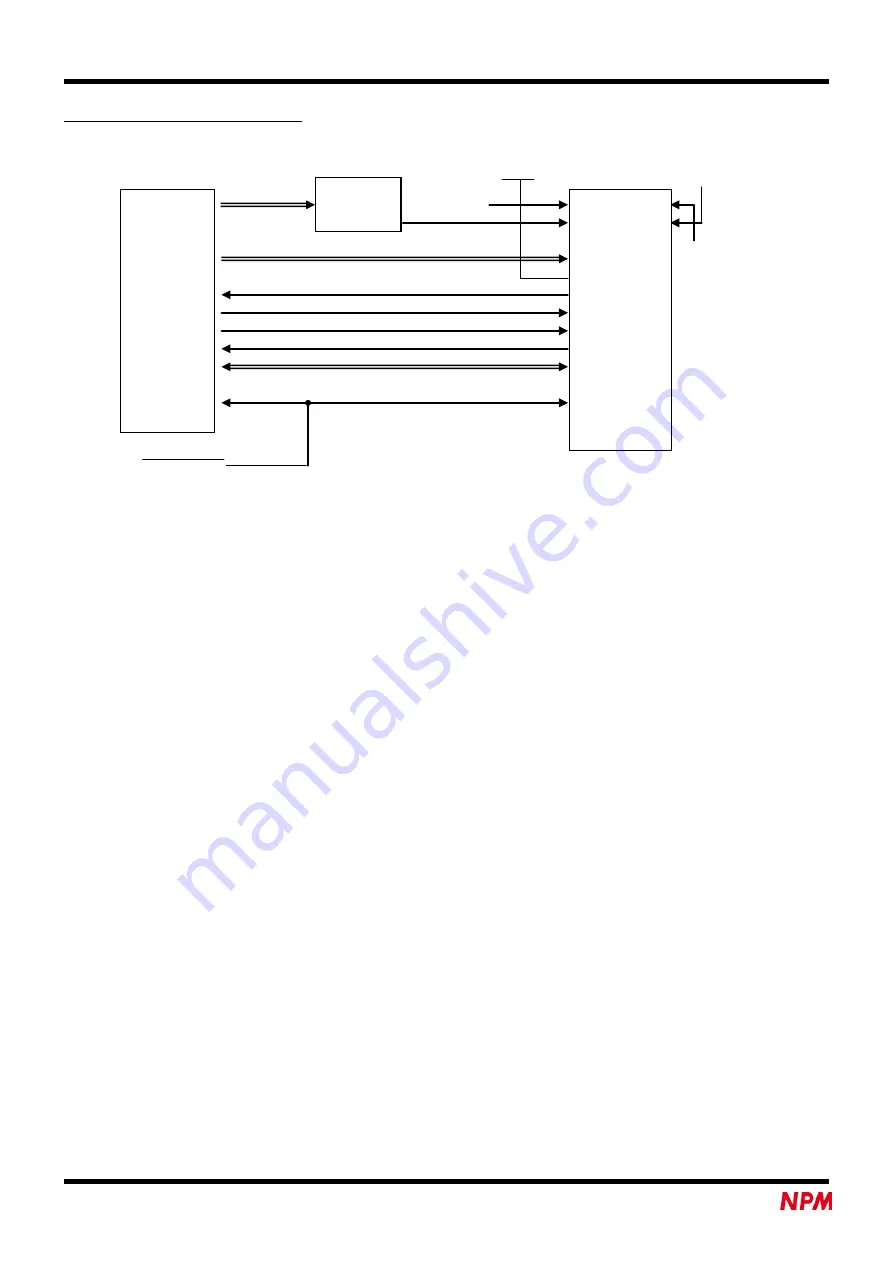

1-1-3. I/F mode 3 (IF1 = L, IF0 = H)

Note 1: When you need to control by only 8 bytes, without using the complete address map, the address

signals can be handled as follows:

A3 to A15: Connect these lines to the decoding circuit and use them to create the

___

CS

signal.

A0 to A2: Connect these lines to A0 to A2 on the center device.

A3 to A8 on the center device should be pulled up.

Decoding

circuit

G9001A

H8 type CPU

CLK

System reset

VDD

GND

VDD

A15 to A9

A8 to A1

____

IRQ

___

RD

____

HWR

_____

WAIT

D15 to D0

______

RESET

CLK

IF1

___

CS

IF0

A8 to A1

A0

____

INT

___

RD

___

WR

____

WRQ

D15 to D0

____

RST

Содержание Motionnet G9001A

Страница 1: ...DA70131 1 3E G9001A G9002A User s Manual Center device I O device Remote I O Remote Motion...

Страница 7: ...DA70131 1 3E I 1 I Center device G9001A User s Manual...

Страница 8: ...DA70131 1 3E I 2...

Страница 50: ...DA70131 1 3E I 44...

Страница 51: ...DA70131 1 3E II 1 II I O device G9002A User s Manual...

Страница 52: ...DA70131 1 3E II 2...

Страница 66: ...DA70131 1 3E II 16...

Страница 67: ...DA70131 1 3E III 1 III Connection Examples and Recommended Environments G9000 Series...

Страница 68: ...DA70131 1 3E III 2...

Страница 87: ...DA70131 1 3E IV 1 IV Software Examples flow chart G9001A...

Страница 88: ...DA70131 1 3E IV 2...