760

Chapter 18

AFCAN Controller

User’s Manual U16580EE3V1UD00

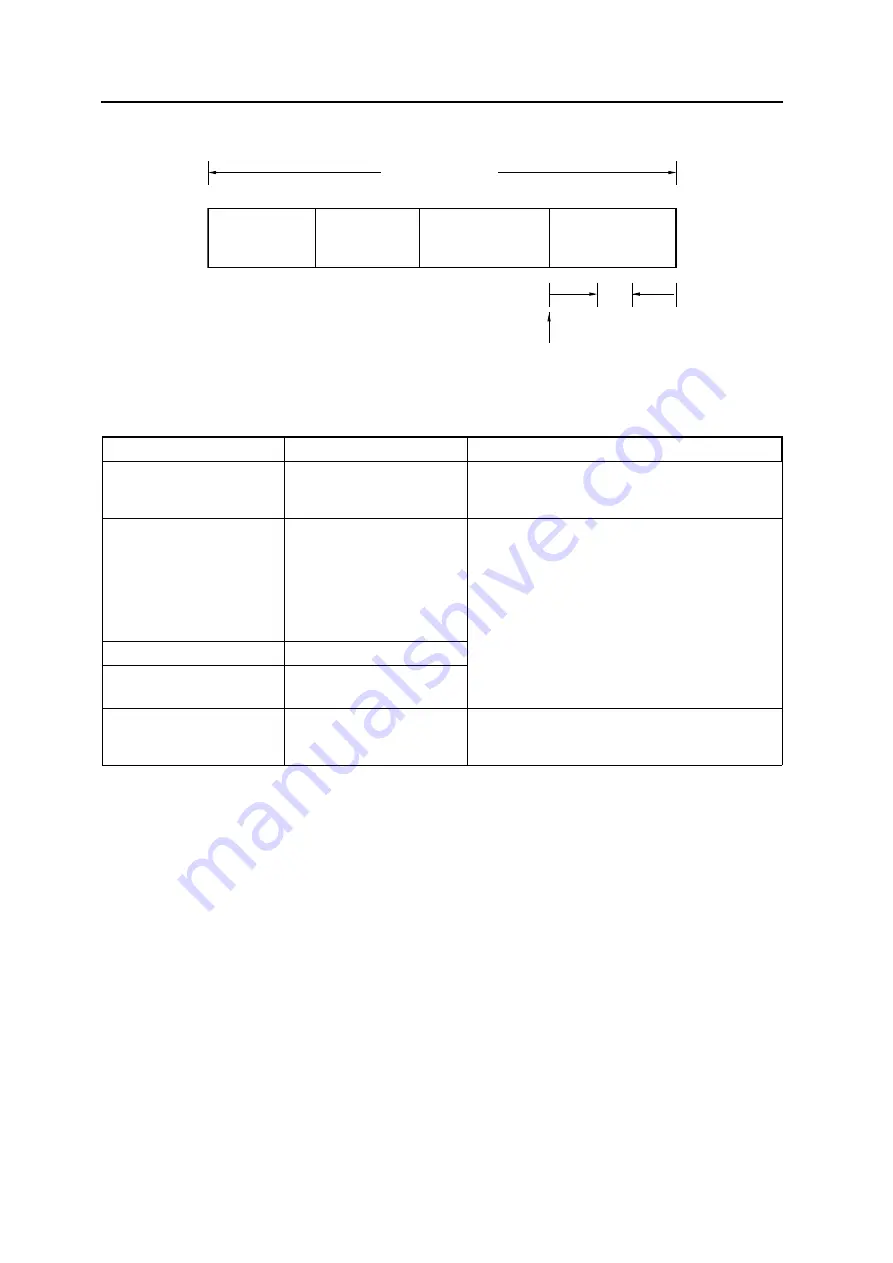

Figure 18-19:

Configuration of data bit time defined by CAN specification

Note:

IPT: Information Processing Time

Table 18-16:

Configuration of data bit time defined by CAN specification

Segment name

Settable range

Notes on setting to conform to CAN specification

Sync segment

(Synchronization segment)

1

This segment starts at the edge where the level

changes from recessive to dominant when

hardware synchronization is established.

Prop segment

Programmable to 1 to 8

or more

This segment absorbs the delay of the output

buffer, CAN bus, and input buffer.

The length of this segment is set so that ACK is

returned before the start of phase segment 1.

Time of prop segment

≥

(Delay of output buffer) +

2

×

(Delay of CAN bus) + (Delay of input buffer)

This segment compensates for an error of data bit

time.

The longer this segment, the wider the permissible

range but the slower the communication speed.

Phase segment 1

Programmable to 1 to 8

Phase segment 2

Phase segment 1 or IPT,

whichever greater

SJW

Programmable from 1TQ to

length of segment 1 or 4TQ,

whichever is smaller

This width sets the upper limit of expansion or

contraction of the phase segment during re-

synchronization.

Phase segment 1

Prop segment

Sync segment

Phase segment 2

Sample point (SPT)

SJW

Data bit time(DBT)

Содержание V850E/PH2

Страница 6: ...6 Preface User s Manual U16580EE3V1UD00...

Страница 16: ...16 User s Manual U16580EE3V1UD00...

Страница 28: ...28 User s Manual U16580EE3V1UD00...

Страница 32: ...32 User s Manual U16580EE3V1UD00...

Страница 84: ...84 Chapter 2 Pin Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 144: ...144 Chapter 3 CPU Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 192: ...192 Chapter 5 Memory Access Control Function PD70F3187 only User s Manual U16580EE3V1UD00 MEMO...

Страница 312: ...312 Chapter 9 16 Bit Timer Event Counter P User s Manual U16580EE3V1UD00 MEMO...

Страница 534: ...534 Chapter 11 16 bit Timer Event Counter T User s Manual U16580EE3V1UD00...

Страница 969: ...969 Chapter 20 Port Functions User s Manual U16580EE3V1UD00 MEMO...

Страница 970: ...970 Chapter 20 Port Functions User s Manual U16580EE3V1UD00...

Страница 976: ...976 Chapter 22 Internal RAM Parity Check Function User s Manual U16580EE3V1UD00 MEMO...

Страница 984: ...984 Chapter 23 On Chip Debug Function OCD User s Manual U16580EE3V1UD00 MEMO...

Страница 1006: ...1006 Chapter 24 Flash Memory User s Manual U16580EE3V1UD00 MEMO...

Страница 1036: ...1036 Chapter 27 Recommended Soldering Conditions User s Manual U16580EE3V1UD00 MEMO...

Страница 1046: ...1046 Appendix A Index User s Manual U16580EE3V1UD00 MEMO...

Страница 1052: ...1052 User s Manual U16580EE3V1UD00...

Страница 1053: ......