1-24

Computer Group Literature Center Web Site

Product Data and Memory Maps

1

Status Register

The MVME5100 implementation of this Register is fully compliant with

the PowerPlus II programming model, with exceptions to bits RD5, RD6

and RD7, as identified in the following table:

An 8-bit status register, accessible through the External Register Set port,

defines the status of the Module.

SYSCON_

System Controller Mode bit. If this bit is set, the module is not the

master of its PCI bus (PCI bus 0). If this bit is cleared, the module

is the master of its PCI bus (PCI bus 0). This bit always reads as

cleared (“0”).

BAUDOUT

This is the baud output clock of the TL16C550 UART, referenced

to the 1.8432 MHz UART oscillator. This signal can be used as a

timing reference.

FUSE

This bit provides the current state of the FUSE signal. If set, at

least one of the planar fuses or polyswitches is open.

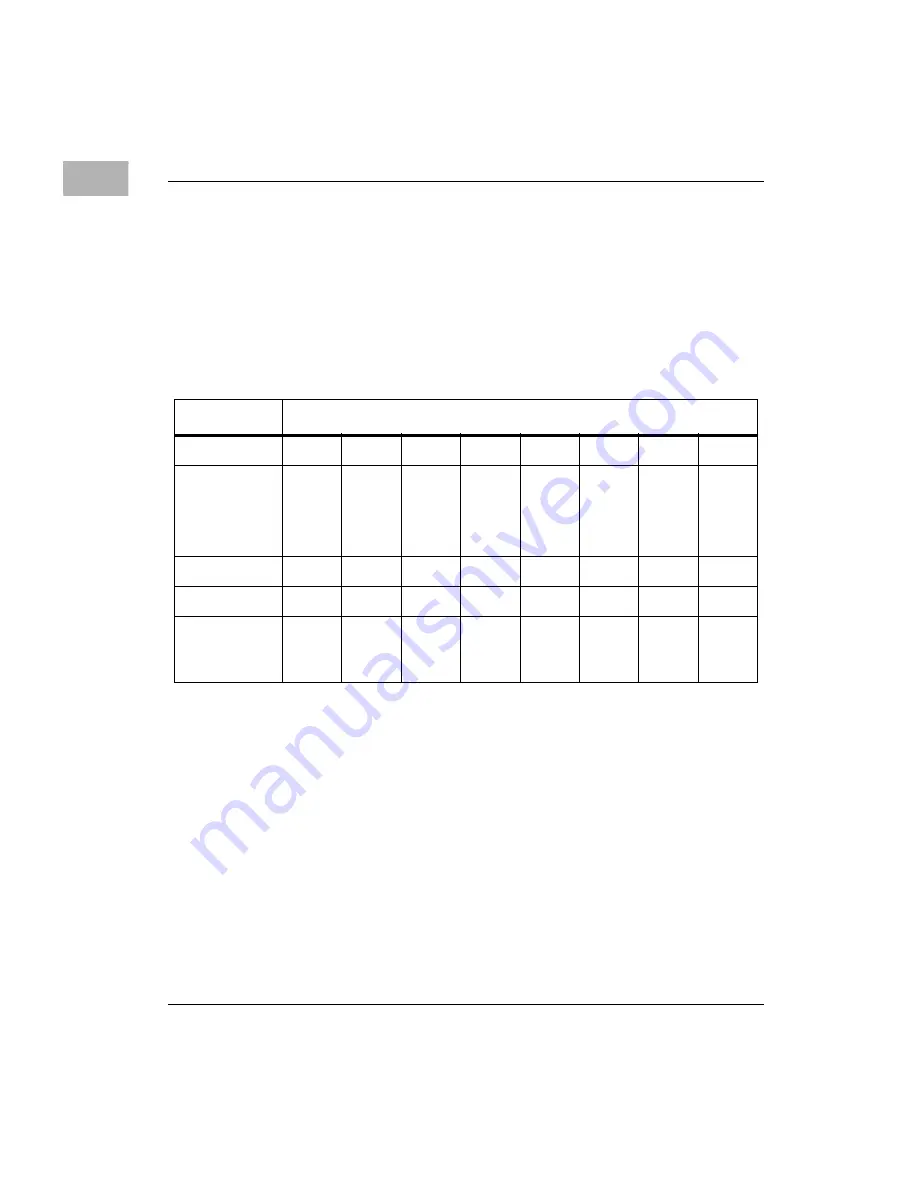

Table 1-11. MVME5100 Status Register

REG

Status Register - FEF88080h

BIT

RD0

RD1

RD2

RD3

RD4

RD5

RD6

RD7

FIELD

FUSE

B

AUDOUT

S

Y

SC

ON_

OPER

R

R

R

R

R

R

R

R

RESET

X

X

X

X

X

X

X

0

REQUIRED

OR

OPTIONAL

X

X

X

X

X

O

R

R

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...