3-46

Computer Group Literature Center Web Site

System Memory Controller (SMC)

3

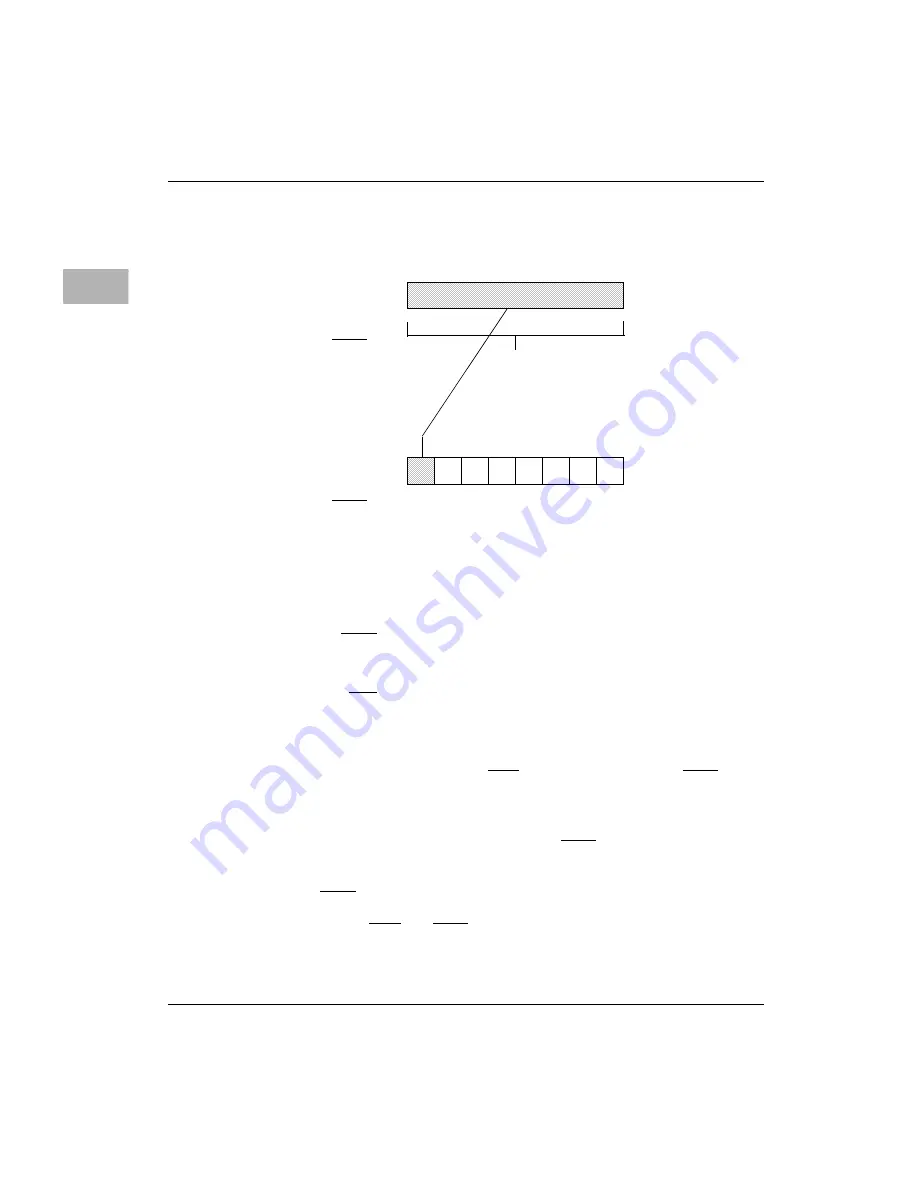

Figure 3-10. Read/Write Check-bit Data Paths

Note that if test software attempts to force a single-bit error to a location

using the rwcb function, the scrubber may correct the location before the

test software gets a chance to check for the single-bit error. This can be

avoided by disabling scrub writes. Also note that writing bad check-bits

can set the elog bit in the Error Logger Register. The writing of check-bits

causes the SMC to perform a read-modify-write to SDRAM. If the location

to which check-bits are being written has a single- or double-bit error, data

in the location may be altered by the write check-bits operation. To avoid

this, it is recommended that the derc bit also be set while the rwcb bit is

set. A possible sequence for performing read-write check-bits is as

follows:

1. Disable scrub writes by clearing the swen bit if it is set.

2. Make sure software is not using DRAM at this point, because while

rwcb is set, DRAM will not function as normal memory.

3. Set the derc and rwcb bits in the Data Control register.

4. Perform the desired read and/or write check-bit operations.

64 bits

0

Normal

View of

Data

Check-bit

View

(rwcb=1)

0

1

2

3

4

5

6

7

(rwcb=0)

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...