2-122

Computer Group Literature Center Web Site

Hawk PCI Host Bridge & Multi-Processor Interrupt Controller

2

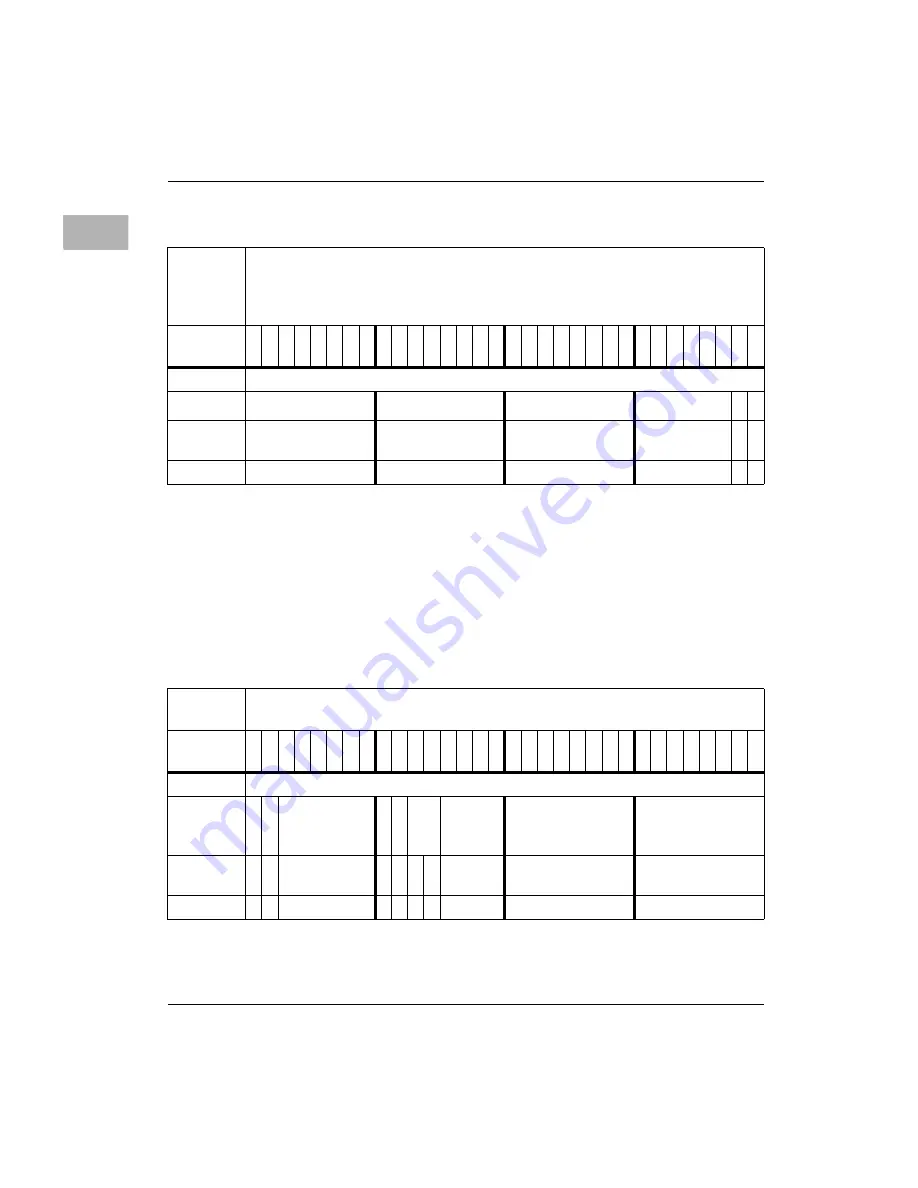

Timer Destination Registers

This register indicates the destinations for this timer’s interrupts. Timer

interrupts operate in the Directed delivery interrupt mode. This register

may specify multiple destinations (multicast delivery).

P1

PROCESSOR 1. The interrupt is directed to processor 1.

P0

PROCESSOR 0. The interrupt is directed to processor 0.

External Source Vector/Priority Registers

Offset

Timer 0 - $01130

Timer 1 - $01170

Timer 2 - $011B0

Timer 3 - $011F0

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

TIMER DESTINATION

P1

P0

Operation

R

R

R

R

R/

W

R/W

Reset

$00

$00

$00

$00

0

0

Offset

Int Src 0 - $10000

Int Src 1-> Int Src15 - $10020 -> $101E0

Bit

3

1

3

0

2

9

2

8

2

7

2

6

2

5

2

4

2

3

2

2

2

1

2

0

1

9

1

8

1

7

1

6

1

5

1

4

1

3

1

2

1

1

1

0 9 8 7 6 5 4 3 2 1 0

Name

EXTERNAL SOURCE VECTOR/PRIORITY

MA

SK

AC

T

PO

L

SE

N

S

E

PRIOR

VECTOR

Operation

R/

W

R

R

R/

W

R/

W

R

R

R/W

R

R/W

Reset

1

0

$000

0

0

0

0

$0

$00

$00

Содержание MVME5100 Series

Страница 1: ...MVME5100 Single Board Computer Programmer s Reference Guide V5100A PG2 September 2001 Edition ...

Страница 16: ...xvi ...

Страница 20: ...xx ...

Страница 28: ...xxviii ...

Страница 62: ...1 34 Computer Group Literature Center Web Site Product Data and Memory Maps 1 ...

Страница 278: ...3 88 Computer Group Literature Center Web Site System Memory Controller SMC 3 ...

Страница 288: ...4 10 Computer Group Literature Center Web Site Hawk Programming Details 4 ...

Страница 320: ...Index IN 12 Computer Group Literature Center Web Site I N D E X ...