Chapter 7. PCI Bus Interface

7-17

PCI Bus Transactions

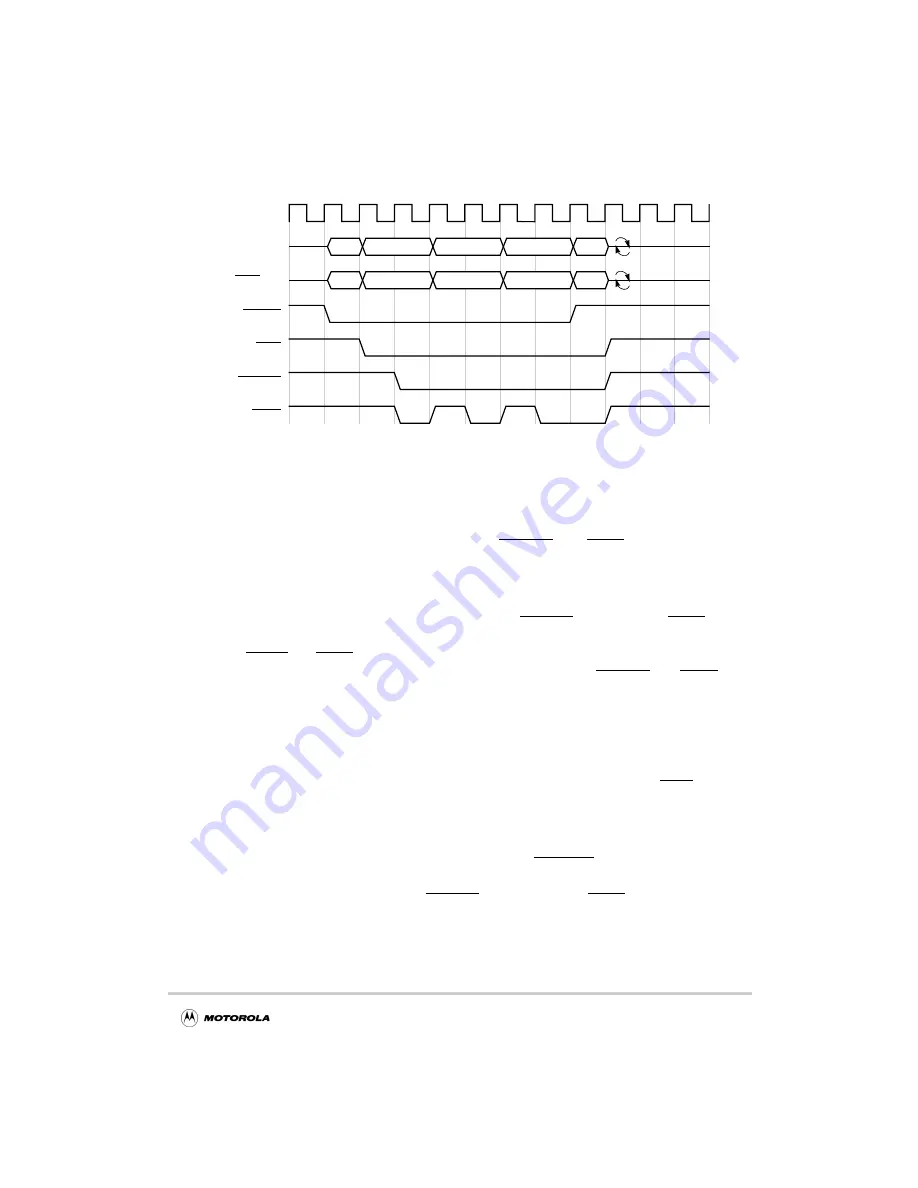

Figure 7-6. PCI Burst Write Transaction

7.4.3 Transaction Termination

A PCI transaction may be terminated by either the initiator or the target. The initiator is

ultimately responsible for concluding all transactions, regardless of the cause of the

termination. All transactions are concluded when FRAME and IRDY are both negated,

indicating the bus is idle.

7.4.3.1 Master-Initiated Termination

Normally, a master initiates termination by negating FRAME and asserting IRDY. This

indicates to the target that the final data phase is in progress. The final data transfer occurs

when both TRDY and IRDY are asserted. The transaction is considered complete when data

is transferred in the last data phase. After the final data phase, both FRAME and IRDY are

negated (the bus becomes idle).

There are three types of master-initiated termination:

•

Completion—Refers to termination when the initiator has concluded its intended

transaction. This is the most common reason for termination.

•

Timeout—Refers to termination when the initiator loses its bus grant (GNTn is

negated), and its internal latency timer has expired. The intended transaction is not

necessarily concluded.

•

Master-abort—An abnormal case of master-initiated termination. If no device

(including the subtractive decoding agent) asserts DEVSEL to claim a transaction,

the initiator terminates the transaction with a master-abort. For a master-abort

termination, the initiator negates FRAME and then negates IRDY on the next clock.

If a transaction is terminated by master-abort (except for a special-cycle command),

the received master-abort bit (bit 13) of the PCI status register is set.

PCI_SYNC_IN

FRAME

IRDY

AD[0:31]

ADDR

DEVSEL

TRDY

C/BE[0:3]

DATA4

DATA1

DATA2

DATA3

Byte enables 1 Byte enables 2

CMD

BEs 4

Byte enables 3

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...