5-26

MPC8240 Integrated Processor User’s Manual

Exception Model

5.5 Exception Model

This section describes the PowerPC exception model and implementation-specific details

of the MPC8240 core.

5.5.1 PowerPC Exception Model

The PowerPC exception mechanism allows the processor to change to supervisor state as a

result of external signals, errors, or unusual conditions arising in the execution of

instructions. When exceptions occur, information about the state of the processor is saved

to certain registers and the processor begins execution at an address (exception vector)

predetermined for each exception. Processing of exceptions occurs in supervisor mode.

Although multiple exception conditions can map to a single exception vector, a more

specific condition may be determined by examining a register associated with the

exception. For example, the DSISR identifies instructions that cause a DSI exception.

Additionally, some exception conditions can be explicitly enabled or disabled by software.

The PowerPC architecture requires that exceptions be handled in program order; therefore,

although a particular implementation may recognize exception conditions out of order,

exceptions are taken in strict order. When an instruction-caused exception is recognized,

any unexecuted instructions that appear earlier in the instruction stream, including any that

have not yet entered the execute stage, are required to complete before the exception is

taken. Any exceptions caused by those instructions are handled first. Likewise, exceptions

that are asynchronous and precise are recognized when they occur, but are not handled until

the instruction currently in the completion stage successfully completes execution or

generates an exception, and the completed store queue is emptied.

Unless a catastrophic condition causes a system reset or machine check exception, only one

exception is handled at a time. If, for example, a single instruction encounters multiple

exception conditions, those conditions are handled sequentially. After the exception handler

handles an exception, the instruction execution continues until the next exception condition

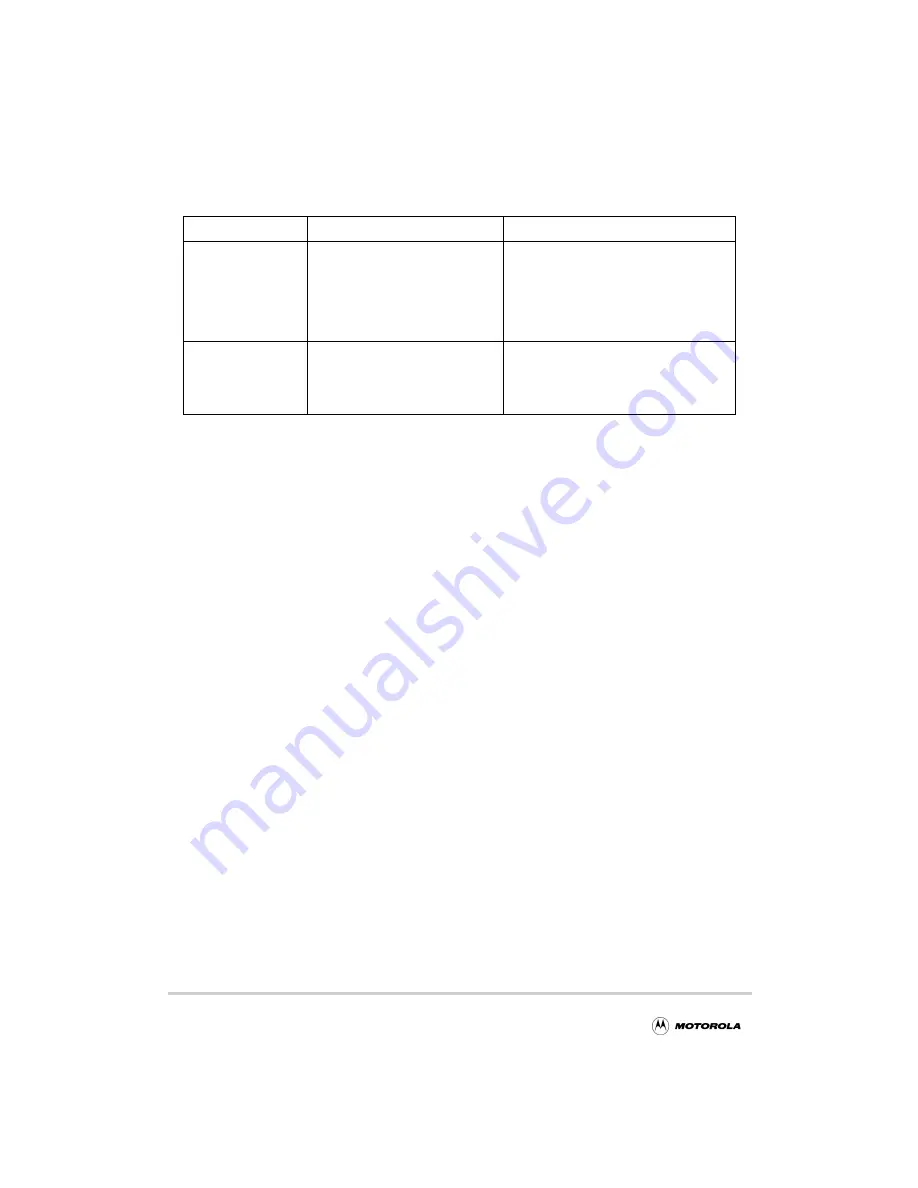

Write-with-flush

Write-with-flush-atomic

Non-locked PCI write to memory or

locked PCI write to memory,

respectively

• If the addressed block is in the exclusive

state, the snoop forces the state of the

addressed block to invalid.

• If the addressed block is in the modified

state, the snoop causes a push of the modified

block out of the cache to memory and changes

the state of the block to invalid.

Write-with-kill

Locked or non-locked PCI write with

invalidate to memory

In a write-with-kill operation, the processor

snoops the cache for a copy of the addressed

block. If one is found the cache block is forced

to the I state, killing modified data that may

have been in the block.

Table 5-6. Transactions Reflected to the Processor for Snooping (Continued)

Snooped Transaction

Condition Detected by CCU

Processor Response

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...