4-52

MPC8240 Integrated Processor User’s Manual

Memory Control Configuration Registers

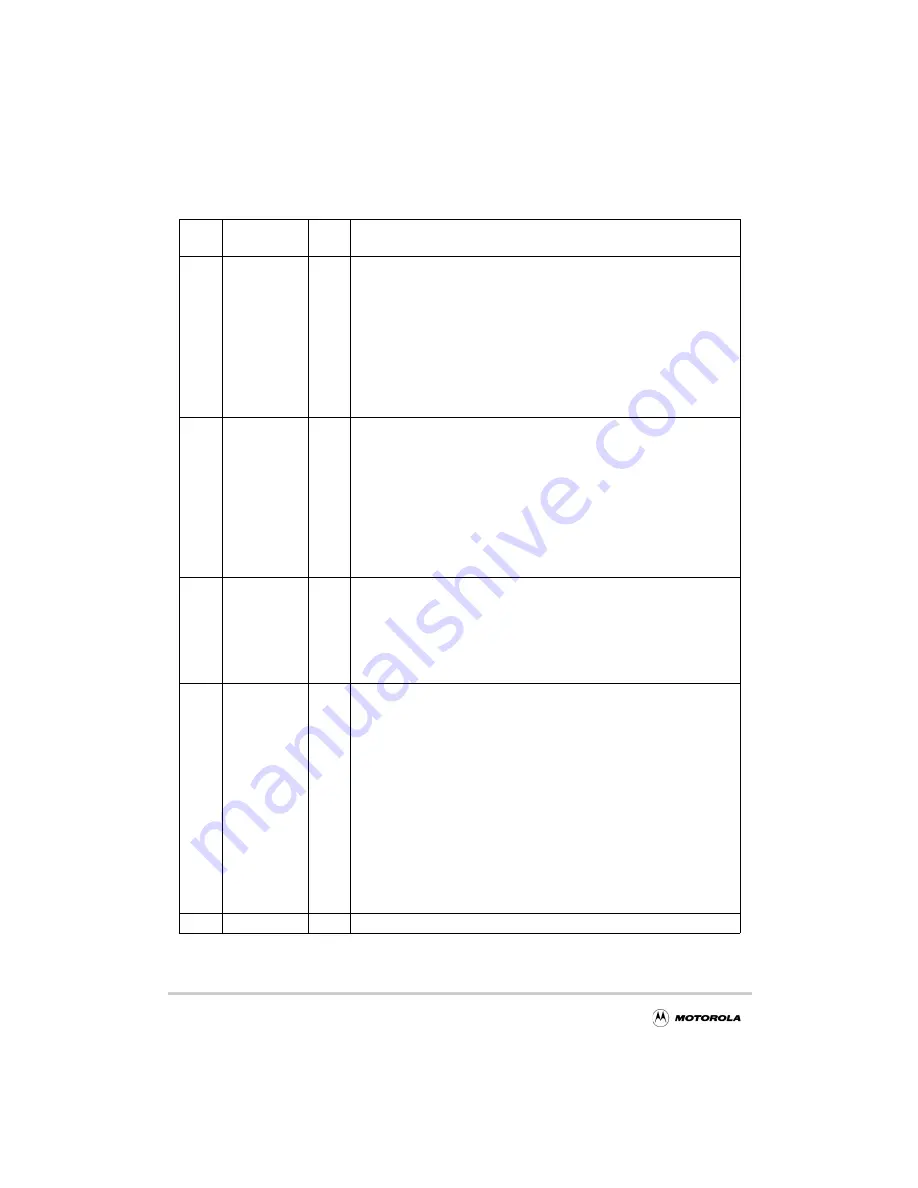

Table 4-41. Bit Settings for MCCR4—0xFC

Bits

Name

Reset

Value

Description

31–28 PRETOACT

0000

Precharge to activate interval. For SDRAM only. These bits control the number

of clock cycles from an SDRAM-precharge command until an SDRAM-activate

command is allowed. See Section 6.2.4, “SDRAM Power-On Initialization,” for

more information.

0001 1 clock

0010 2 clocks

0011 3 clocks

...

...

1111 15 clocks

0000 16 clocks

27–24

ACTOPRE

0000

Activate to precharge interval. For SDRAM only. These bits control the number

of clock cycles from an SDRAM-activate command until an SDRAM-precharge

command is allowed. See Section 6.2.4, “SDRAM Power-On Initialization,” for

more information.

0001 1 clock

0010 2 clocks

0011 3 clocks

...

...

1111 15 clocks

0000 16 clocks

23

WMODE

0

Length of burst for 32-bit data. Applies to 32-bit data path mode only.

Determines whether the burst ROMs can accept eight beats in a burst or only

four. In 32-bit data path mode, burst transactions require data beats. If the burst

ROM can only accept four beats per burst, the memory controller must perform

two transactions to the ROM.

0 Four beats per burst (default)

1 Eight beats per burst

22

BUF_TYPE[0]

0

Most significant bit of the memory data bus buffer type field. BUF_TYPE[0] is

used with bit 20 below (BUF_TYPE[1]) to configure the internal memory data

path buffering scheme as follows:

BUF_TYPE[0–1]:

00 Flow through buffer mode (default)

01 Registered buffer mode

10 In-line buffer mode; SDRAM only

11 Reserved

The MPC8240 must be configured for in-line buffer mode in order to use the

in-line ECC/parity logic for SDRAM. The in-line ECC and parity hardware allow

the MPC8240 to check/generate parity on the internal peripheral logic bus and

check/correct/generate ECC or parity on the external SDRAM memory bus. See

Section 6.2.3, “SDRAM Memory Data Interface,” and Section 6.3.3,

“FPM or EDO Memory Data Interface,” for more information.

21

—

0

Reserved

Содержание MPC8240

Страница 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Страница 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Страница 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Страница 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Страница 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Страница 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Страница 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Страница 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Страница 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Страница 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Страница 516: ...16 14 Watchpoint Trigger Applications ...

Страница 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Страница 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Страница 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...