SA.45s Chip-Scale Atomic Clock

SA.45s CSAC User Guide Revision D

15

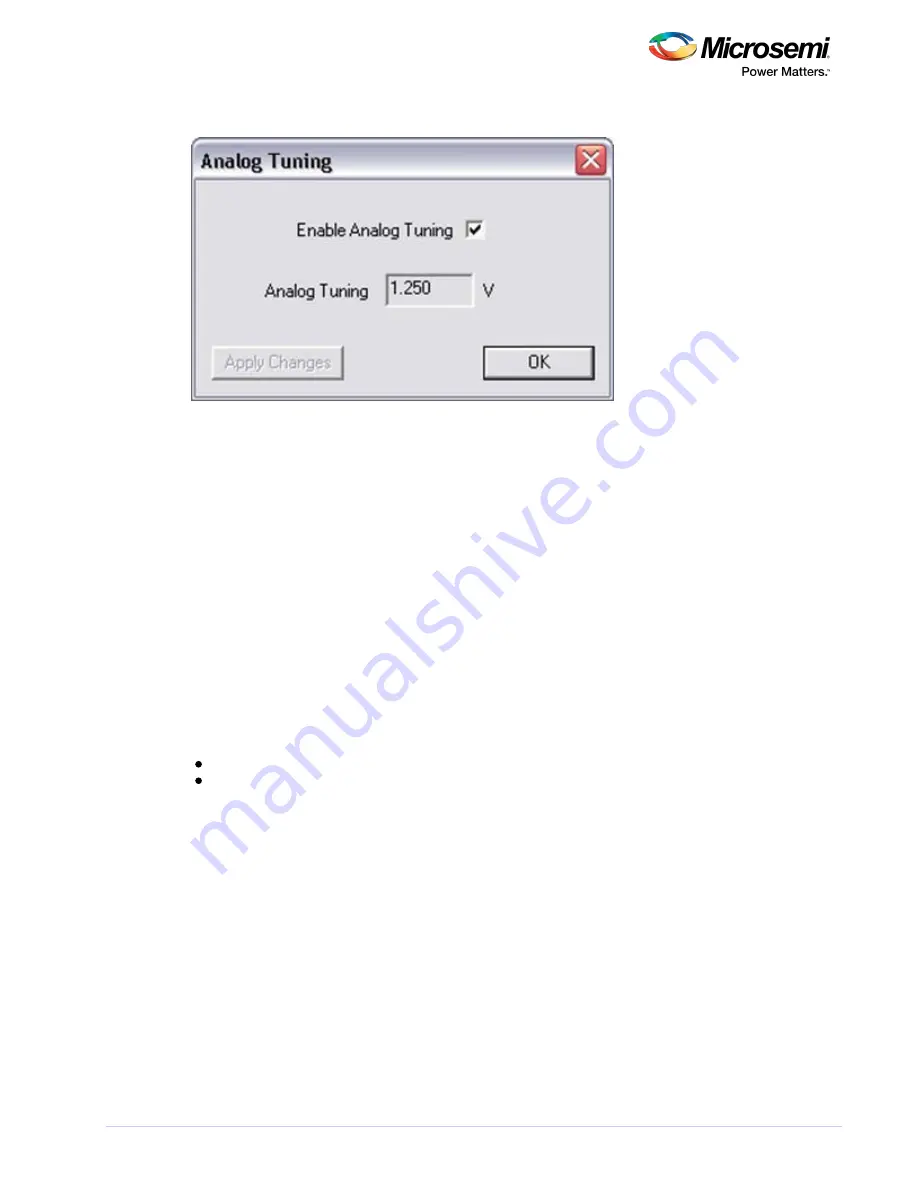

Figure 9 • CSACdemo Analog Tuning Panel

When analog tuning is enabled, the voltage present on pin 1 is displayed in the Analog Tuning field and

also reflected in the current reported value of steer on the main panel. To enable or disable analog

tuning, select

checkbox and click

.

Enable Analog Tuning

Apply Changes

3.3.12

Ultra-Low Power Operating Mode

The majority of the power in the CSAC is consumed by the physics package and microwave synthesizer.

In ultra-low power (ULP) mode, the physics package and synthesizer can be disabled for a user-specified

length of time, during which the CSAC operates as a free-running TCXO. Periodically, the atomic clock

portion of the CSAC is powered on (again for a user-specified amount of time) and the TCXO is re-

calibrated to the atomic frequency. Operating in this mode, the CSAC exhibits the short-term

performance of a TCXO with good long-term stability at significantly lower power compared to standard

mode. For example, if the atomic clock portion is only powered on for 5 minutes out of every hour (2

minutes for lock acqui 3 minutes of run time), then the time-averaged power of the CSAC may be

<30 mW.

Between calibration cycles, the CSAC in ULP mode exhibits the performance characteristics of a free-

running TCXO and therefore exhibits significantly higher short-term frequency drift and environmental

(temperature and vibration) sensitivity than a normally-operating CSAC. For this reason, ULP mode is

principally recommended only for applications that:

Require long-term timing performance, rather than short-term frequency or time stability.

Have a very stable environment (temperature and vibration).

Note: Due to the unique behavior and configurability of ULP, the datasheet performance specifications

for the SA.45s CSAC cannot be guaranteed while in ULP mode. The CSAC has short-term drift

performance of a low cost low performance TCXO. Contact Microsemi for additional assistance in

evaluating and optimizing ULP for your specific application.

The following illustration shows an example of a CSAC operating in ULP mode, with wake-time = 300 s (5

min) and sleep-time = 3300 s (55 min).

Содержание SA.45s

Страница 1: ...User Guide SA 45s Chip Scale Atomic Clock...