REL 1.2

Page 60 of 82

i.MX6 Qseven PMIC SOM Hardware User Guide

iWave Systems Technologies Pvt. Ltd.

2.10

Optional Features

i.MX6 Qseven PMIC SOM has PCB footprint option for some features which are not supported by default. These

optional features are explained in the following sections.

To add any of these optional features in i.MX6 Qseven PMIC SOM, please contact iWave.

2.10.1

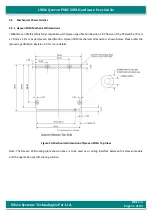

NAND Flash

i.MX6 Qseven PMIC SOM supports NAND flash memory as mass storage and also can be used as boot device. This is

connected to NAND flash controller of the i.MX6 CPU and operates at 3.3 voltage level. This is the optional feature

and will not be populated in default configuration.

Note: If NAND flash feature is required in the SOM, eMMC flash on SOM and signals to Qseven Pins 17, 19, 44, 46, 47,

53, 54, 55, 56, 70, 111, 112 & 156 cannot be used.

2.10.2

RTC Controller

i.MX6 Qseven PMIC SOM by default supports RTC from i.MX6 CPU. But i.MX6 RTC controller draws more power from

VCC_RTC coin cell power input (when VCC is off) and could drain the coin cell faster. So i.MX6 Qseven PMIC SOM

optionally supports external RTC Controller “BQ32000DR” On-SOM which will draw very less power compare to

i.MX6 RTC controller.

External RTC Controller is connected to the i.MX6 CPU through I2C2 Interface and operates at 3.3V voltage level. In

SOM power off condition, this device will take power from Qseven Edge (VCC_RTC) coin cell power input (Pin 193)

and continues to keep the current time. This is the optional feature and will not be populated in default

configuration.