Application Note

13 of 23

V 1.1

2020-11-09

CoolGaN™ 600 V half-bridge evaluation platform featuring GaN

EiceDRIVER™

Setup and use

4.3

Input PWM generator connections and settings

The PWM input is the logic command to the half-bridge output: when the PWM input is high, the half-bridge

output V

sw

is at its high state (connected to the V

in+

bus). Conversely, when the PWM input command is at logic

low, the half-bridge output V

sw

is at 0 (-V

in

). The input is an MMCX coaxial connector terminated in 50 Ω.

Recommended signal/pulse generator settings are fastest rise/fall time, low level of 0 V and high-level of 3.5 V.

The pulse generator can be set to pulse or burst-mode for double-pulse testing, or continuous operation for

buck or boost modes, within the constraints of the warnings given in sections 4 and 4.2.3.

4.4

Measurement points

The evaluation board has 6 test points for connecting an oscilloscope to look at various signals. The test points

are either a through-hole pad-pair, or an MMCX connector. The pad-pairs have a letterscreen symbol that

identifies which pads are signal and reference (common): The signal pad is designated by the ~ symbol, and the

reference pad is designated by the

ꓕ

symbol.

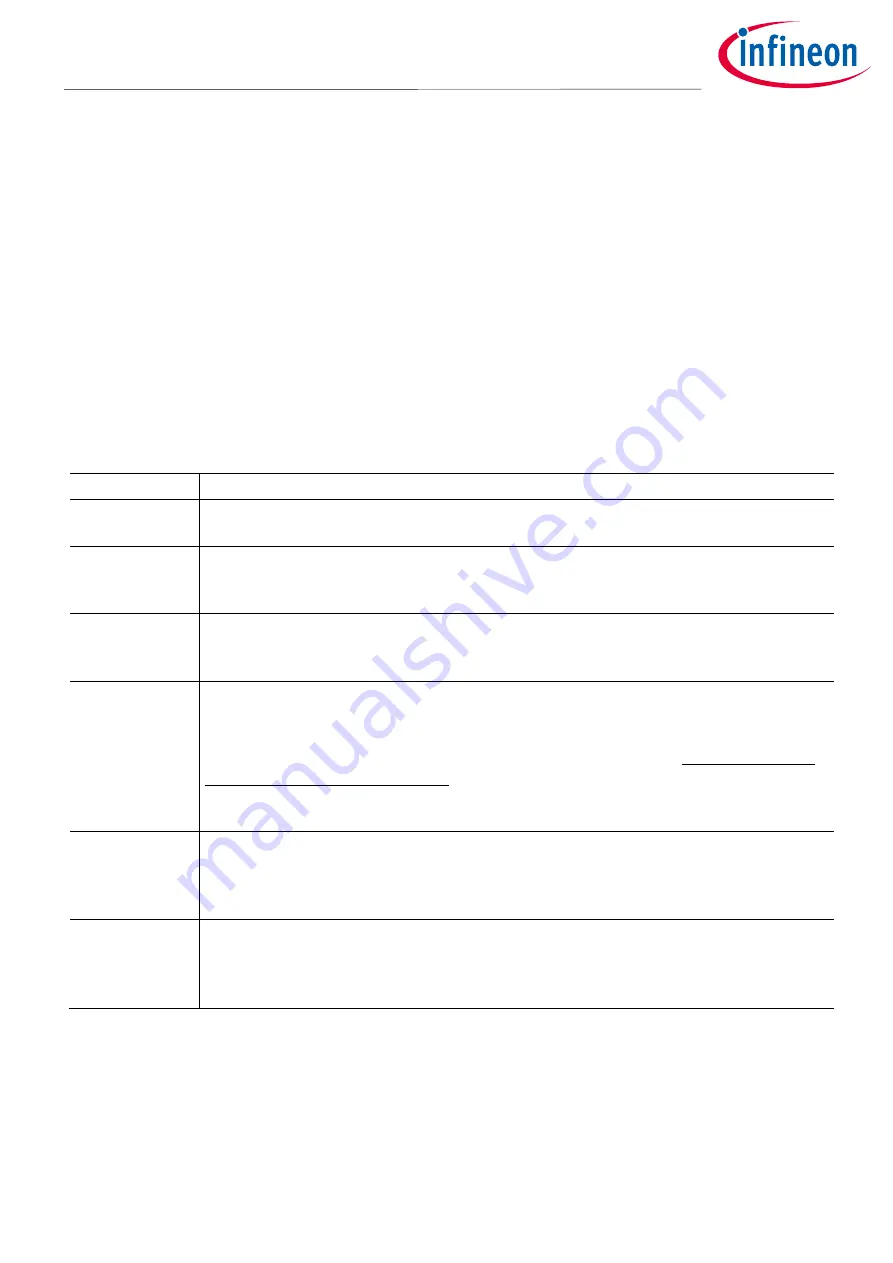

Table 2

Test Point Label Description

TP4

PWM input – parallel to J1. For use in verifying the proper logic drive levels and timing

into the 50 Ω termination. Typical levels here should be 0 – 3.5 V

TP11

PWM input signal to the Schmitt trigger input of the high-side driver IC (U1). The rising-

edge of this signal is delayed from TP4 by the deadtime circuit so it has an exponential

risetime characteristic. Voltage level is standard 5 V AHCT logic level.

TP21

PWM input signal to the Schmitt trigger input of the low-side driver IC (U2). The rising-

edge of this signal is delayed from TP4 by the deadtime circuit so it has an exponential

risetime characteristic. Voltage level is standard 5 V AHCT logic level.

TP1

High-side gate voltage: signal is the gate of Q1, reference is the Kelvin source of Q1. This

test point is an MMCX connector and is designed to be directly connected to the input of a

Tektronix IsoVue isolated probe. Note that the reference point (the barrel of TP1 MMCX

connector) is essentially the output switch-node of the half-bridge so the common-mode

voltage is a fast high-voltage signal – do not use a non-isolated probe on TP1 or

damage will occur. The common-mode voltage is 0-V

in+

, and the differential-mode

measured signal at this point is typically in the range of -8 V to +4 V.

TP2

Low-side gate voltage: signal is the gate of Q2, reference is the Kelvin source of Q2. Since

the reference is the Kelvin-source, there is some common-mode voltage bounce between

this test point reference and “ground” (V

in-

the reference point for TP3). See

recommendations in section 4.1

TP3

This is the test-point to observe the half-bridge switch-node output. Since the bus voltage

is typically in the range of 350 – 400 V, be sure to use a voltage probe with appropriate

voltage rating. We recommend the Tektronix TPP0850 50X high-voltage 800 MHz probe

with its short ground pin. TP3 diameter and spacing will accommodate this probe.

4.5

Power-up and power-down sequencing

The gate drivers are designed to keep V

GS

below the turn-on threshold even if they are unpowered. Regardless,

it is good practice to make sure the 5 volt power (and thus the gate drivers) is always applied before powering-

up the high voltage bus. Conversely, power-down the high-voltage bus before powering-down the 5 volt

supply. Recommended current limit on the 5 volt lab supply is 300 mA, and on the high-voltage supply, it

depends on the expected load power. For basic double-pulse testing, even to 35 A peak, the HV supply can be