3. Processor Bus Interface

98

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

The data parity bits, PB_DP[0:7], are driven to the correct values for even or odd parity by the PB slave

during reads and checked during writes.

The detection of a data parity error does not affect the transaction and data is still forwarded to the

destination bus. See

“Interrupt Handling” on page 145

for a full

description of error logging support and associated interrupt mapping options.

Special Parity Requirements with the PowerQUICC II

Address parity and data parity must be specially programmed in a joint

PowerSpan II and PowerQUICC II application.

In a joint application all memory accesses from the PowerQUICC II to

PowerSpan II must be routed through the internal memory controller on the PowerQUICC II. When the

data is passed through the memory controller both address parity and data parity can be used in the

system.

If accesses do not pass through the memory controller of the PowerQUICC II before reaching

PowerSpan II, and PowerSpan II has either or both address and data parity enabled, then PowerSpan II

reports parity errors on the transaction.

To enable or disable address parity in PowerSpan II, set the Address Parity Enable (AP_EN) bit in the

“Processor Bus Slave Image x Control Register” on page 287

.

To enable or disable data parity in PowerSpan II, set the Data Parity Enable (DP_EN) bit in the

“Processor Bus Slave Image x Control Register” on page 287

.

3.3.3

Terminations

The following sections describe the terminations and exception handling supported by PowerSpan II.

3.3.3.1

PB Slave Termination

The PB slave uses the following pins to indicate termination of individual data beats and/or data tenure:

•

Address Retry (PB_ARTRY_): This signal terminates the entire address and data tenure and

schedules the transaction to be rerun. No data is transferred, even if asserted coincidentally with

PB_TA/PB_DVAL_, as in the case of a third party address retry.

•

Transfer Acknowledge (PB_TA_): This signal is asserted by the PowerSpan II PB Slave to indicate

the successful transfer of a single beat transaction, or each 8-byte quantity transferred for a burst.

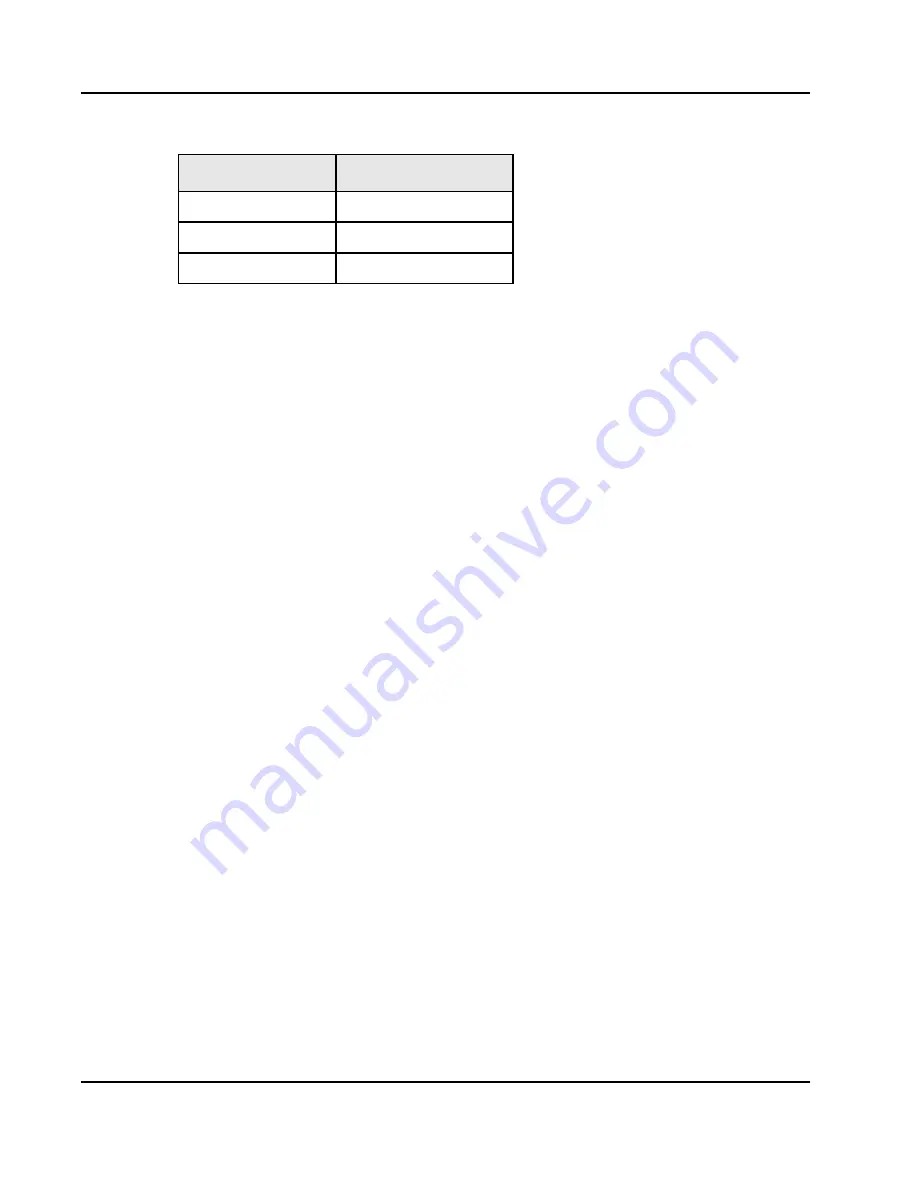

PB_D[40:47]

PB_DP[5]

PB_D[48:55]

PB_DP[6]

PB_D[56:63]

PB_DP[7]

Table 19: PowerSpan II PB Data Parity Assignments

Data Bus

Data Parity

Содержание PowerSpan II

Страница 8: ...Contents 8 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 14: ...List of Tables 14 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 18: ...About this Document 18 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 82: ...2 PCI Interface 82 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 112: ...3 Processor Bus Interface 112 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 156: ...7 Interrupt Handling 156 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 380: ...12 Register Descriptions 380 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 394: ...14 Package Information 394 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 414: ...15 AC Timing 414 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 416: ...16 Ordering Information 416 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 420: ...A Hardware Implementation 420 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 428: ...B Typical Applications 428 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...

Страница 432: ...Glossary 432 PowerSpan II User Manual 80A1010_MA001_09 Integrated Device Technology www idt com ...