Rev. 1.00

103 of ���

�an�a�� 1�� �01�

Standard 8051 8-Bit Flash MCU

HT85F2260/HT85F2270/HT85F2280

Interrupts

Interrupts

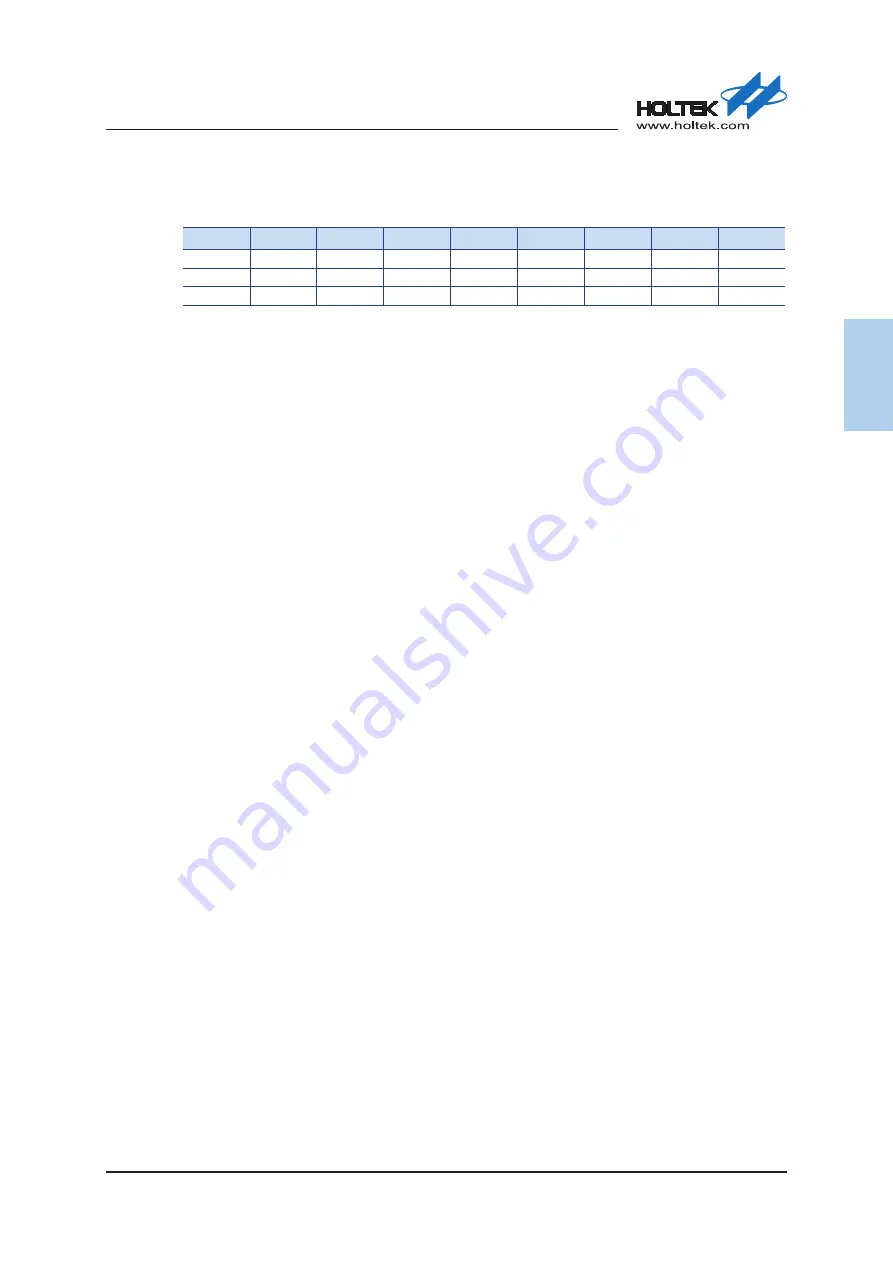

I2CCON Register

SFR Address: D8h

Bit

7

6

5

4

3

2

1

0

Name

—

ENS1

STA

STO

SI

AA

—

—

R/W

—

R/W

R/W

R/W

R

R

—

—

POR

—

0

0

0

0

0

—

—

Bit 7

Unimplemented, read as "0"

Bit 6

ENS1:

I

2

C Enable Control

Described elsewhere

Bit 5

STA:

I

2

C Start flag

Described elsewhere

Bit 4

STO:

I

2

C Stop flag

Described elsewhere

Bit 3

SI:

I

2

C Interrupt Request flag

0: No request

1: Interrupt request

The SI bit is set by hardware when one of the 25 possible I

2

C states takes place. This bit

must be cleared using the application program.

Bit 2

AA:

I

2

C Acknowledge Indication flag

Described elsewhere

Bit 1~0

Unimplemented, read as "0"

Interrupt Operation

A Timer Counter overflow, an active edge or level on the external interrupt pin, a comparator

output changes state or A/D conversion completion etc, will all generate an interrupt request by

setting their corresponding request flag. When this happens, if the interrupt enable bit is set, then

the Program Counter, which stores the address of the next instruction to be executed, will be

transferred onto the stack. The Program Counter will then be loaded with a new address which

will be the value of the corresponding interrupt vector. The microcontroller will begin then fetch

its next instruction from this interrupt vector. The instruction at this vector will jump to another

section of program which is known as the interrupt service routine. Here is located the code to

control the appropriate interrupt. The interrupt service routine must be terminated with a RETI

instruction, which retrieves the original Program Counter address from the stack and allows the

microcontroller to continue with normal execution at the point where the interrupt occurred.

The various interrupt enable bits, together with their associated request flags, are shown in the

following diagram with their order of priority. The interrupts are assigned into groups. Interrupts

with higher priority can stop lower priority ones. All interrupts are categorised into 19 groups and

4 priority levels, setup using the IP0 and IP1 registers.