APEX

™

Exciter Incorporating FLO

™

Technology

Details of the System Setup Screens

Navigating the LCD Display Screens

26

04s30

0.fm

03/08/07

888-2604-001

Page: 3-49

WARNING: Disconnect primary power prior to servicing.

3.6.7.2

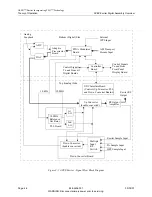

FPGA Configure 2/5

FPGASetup2.bmp

Figure 3-41 FPGA Configure 2/5

FPGA Configure 2/5 consists of registers whose values are written immediately to the

FPGA when changed through the GUI and other software parameters.

No FPGA re-initialization occurs when these registers and parameters are changed.

The parameters of the FPGA Configure 2/5 screen are as follows.

•

SFN Mode:

Indication is On or Off

•

SFN Limit:

Software parameter, time in microseconds, range 0-999)

•

1PPS Mute Delay:

Displayed in minutes, with a range 0 to 2000.

When the GPS 1PPS signal loss (shown in the Main Screen > Status > Digital Pro-

cessing > FLO FPGA Registers > GPS and Clock Status screen) exceeds the 1PPS

Mute Delay time, the GPS 1PPS Loss indication in the GPS and Clock Status screen

will change to YES (in red) and cause the exciter to mute.

•

PRBS On/Off:

Indication is On or Off

•

TDM1 Null:

Indication is On or Off. This register is not part of the initialization se-

quence.)

•

FPGA Access

has following functions:

• From AC restart, the FPGA access mode is always enabled, but it can be dis-

abled at any time.

• In the FPGA access disable mode:

The periodic access to the FPGA will be blocked, except for flywheel and in-

ternal GPS.

FPGA will not be initialized by SW

LCD interface to FPGA is not blocked, the user must decide to decide to

change the configuration from GUI.

The mute to exciter cannot be performed by SW since it now has no access

to the FPGA.