APEX

™

Exciter Incorporating FLO

™

Technology

Theory of Operation

APEX Exciter Analog Assembly Overview

Page: 4-10

888-2604-001

03/08/07

WARNING: Disconnect primary power prior to servicing.

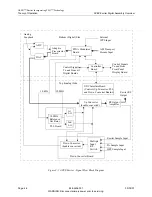

Figure 4-6 Analog Assembly Detailed Block Diagram.

4.4.3

PLL Board - A4

The PLL (phase lock loop) board generates the two local oscillator signals needed for the

up and down converter boards. A 10 MHz reference oscillator is required to keep the two

local oscillators on frequency.

4.4.3.1

10 MHz Reference

Refer to Figure 4-7. The primary 10 Mhz reference is generated by an OCXO. It is buffered

and three outputs are available. One (J11) is for the first and second local oscillators, one

(J8) is for the FPGA Modulator board (a feedback reference which is used to generate the

16 bit DAC number which controls the OCXO frequency), and one (without a connector)

for an on board PLL, which is an alternate method of control for the OCXO oscillator

frequency. This OCXO runs in either of two modes,

The 10 MHz oscillator can be locked by either of two methods.

• This method is via a control voltage form the DAC.The DAC number is supplied

from the controller board, and locks the 10 MHz oscillator to the 1 PPS (pulse per

second) output of a GPS Satellite. This is the mode used in the Apex Mobile exciter.

• The alternate method is via an external 10 kHz from the FPGA modulator board.

1

st

LO

140MHz

SAW

Filter

2

nd

LO

Variable

Gain

Amp

55-75MHz

Filter

Low Band

Amp

Detector

Coupler

Gain

Control

RF

Out

From

Controller

170-230MHz

Filter

High Band

470-860MHz

Filter

UHF

Switch

Switch

140MHz

BPF

50MHz

LPF

Variable

Gain

Attenuator

Sample 1

10.76MHz

Input

Switch

Sample 2

Sample 3

D/A

Converter

To

A/D

Sample 4

10MHz

Ref

10.76MHz

Clock

External

10MHz

D/A

Converter

De-

code

Down Converter Gain

Down Converter Gain

Set Output Power

A/D

Converter

Read Output Power

Band

Select

Channel Select

2

nd

LO

Program

1

st

LO

Program

Band Select

Channel Select

Set Output Power

1

st

LO Program

2

nd

LO Program

Read Output Power

Select Sample

Select sample

1

st

LO

Lock

2nd LO

Lock

1

st

LO Lock

2

nd

LO Lock

External

Ref Present

D/A

Converter

Ext. 10MHz Present

Mute

Mute

Mute

UDCS

SCLK

MISO

MOSI

30MHz

LPF

Detector

Danielsons

Last Revision

10/6/00

Detector

Detector

Gain

Control

11.1 MHz

IF Input

10 kHz

From FPGA

Modulator