13 I

2

C (I2C)

13-4

Seiko Epson Corporation

S1C17M12/M13 TECHNICAL MANUAL

(Rev. 1.2)

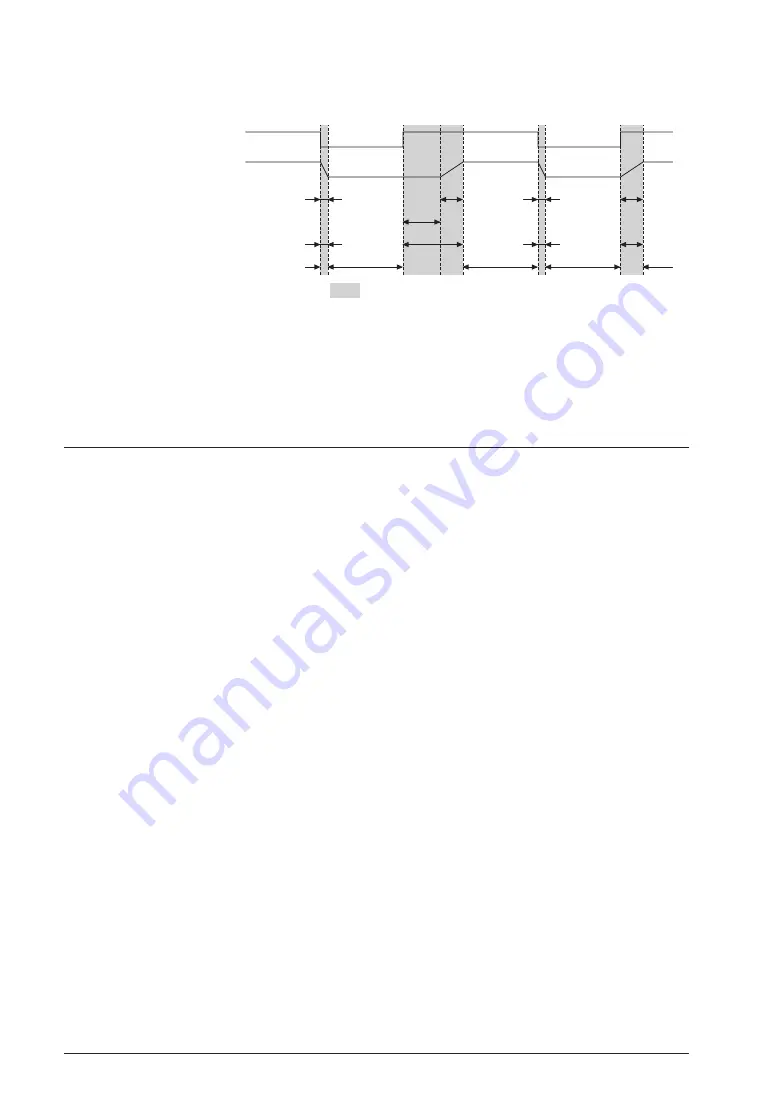

Baud rate generator clock output and operations for supporting clock stretching

Figure 13.3.3.1 shows the clock generated by the baud rate generator and the clock waveform on the I

2

C bus.

SCLO (internal signal)

SCLn (external pin)

SCL rising/falling period

Clock stretching period by another I

2

C device

Baud rate generator counting suspended period

Baud rate generator counting period

Period in which the internal and external statuses are not matched

Figure 13.3.3.1 Baud Rate Generator Output Clock and SCLn Output Waveform

The baud rate generator output clock SCLO is compared with the SCL

n

pin status and the results are returned

to the baud rate generator. If a mismatch has occurred between SCLO and SCL

n

pin levels, the baud rate gen-

erator suspends counting. This extends the clock to control data transfer during the SCL signal rising/falling

period and clock stretching period in which SCL is fixed at low by a slave device.

13.4 Operations

13.4.1 Initialization

The I2C Ch.

n

should be initialized with the procedure shown below.

When using the I2C in master mode

1. Configure the operating clock and the baud rate generator using the I2C

n

CLK and I2C

n

BR registers.

2. Assign the I2C Ch.

n

input/output function to the ports. (Refer to the “I/O Ports” chapter.)

3. Set the following bits when using the interrupt:

- Write 1 to the interrupt flags in the I2C

n

INTF register.

(Clear interrupt flags)

- Set the interrupt enable bits in the I2C

n

INTE register to 1. (Enable interrupts)

4. Set the following I2C

n

CTL register bits:

- Set the I2C

n

CTL.MST bit to 1.

(Set master mode)

- Set the I2C

n

CTL.SFTRST bit to 1.

(Execute software reset)

- Set the I2C

n

CTL.MODEN bit to 1.

(Enable I2C Ch.

n

operations)

When using the I2C in slave mode

1. Set the following I2C

n

MOD register bits:

- I2C

n

MOD.OADR10 bit

(Set 10/7-bit address mode)

- I2C

n

MOD.GCEN bit

(Enable response to general call address)

2. Set its own address to the I2C

n

OADR.OADR[9:0] (or OADR[6:0]) bits.

3. Assign the I2C Ch.

n

input/output function to the ports. (Refer to the “I/O Ports” chapter.)

4. Set the following bits when using the interrupt:

- Write 1 to the interrupt flags in the I2C

n

INTF register.

(Clear interrupt flags)

- Set the interrupt enable bits in the I2C

n

INTE register to 1. (Enable interrupts)

5. Set the following I2C

n

CTL register bits:

- Set the I2C

n

CTL.MST bit to 0.

(Set slave mode)

- Set the I2C

n

CTL.SFTRST bit to 1.

(Execute software reset)

- Set the I2C

n

CTL.MODEN bit to 1.

(Enable I2C Ch.

n

operations)