3 CPU AND DEBUGGER

3-2

Seiko epson Corporation

S1C17F13 TeChniCal Manual

(Rev. 1.0)

CPU Core

3.2

CPU Registers

3.2.1

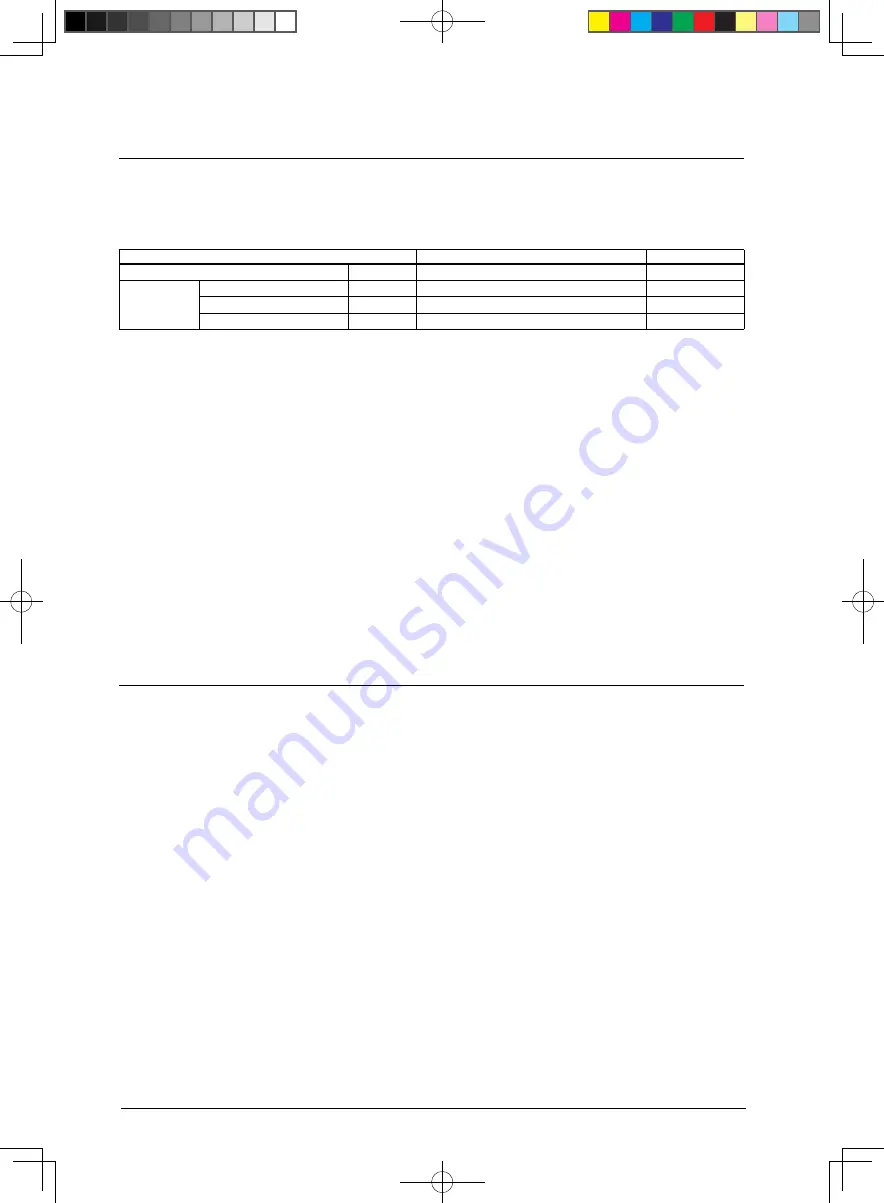

The CPU includes eight general-purpose registers and three special registers (Table 3.2.1.1).

2.1.1 Initialization of CPU Registers

Table 3.

CPU register name

Initial

Reset

General-purpose registers

R0 to R7

0x000000

H0

Special

registers

Program counter

PC

The reset vector is automatically loaded.

H0

Stack pointer

SP

0x000000

H0

Processor status register PSR

0x00

H0

For details on the CPU registers, refer to the “S1C17 Family S1C17 Core Manual.” For more information on the

reset vector, refer to the “Interrupt Controller” chapter.

Instruction Set

3.2.2

The CPU instruction codes are all fixed to 16 bits in length which, combined with pipelined processing, allows the

most important instructions to be executed in one cycle. For details on the instructions, refer to the “S1C17 Family

S1C17 Core Manual.”

Reading PSR

3.2.3

The PSR contents can be read through the MSCPSR register. Note, however, that data cannot be written to PSR

through the MSCPSR register.

I/O Area Reserved for the S1C17 Core

3.2.4

The address range from 0xfffc00 to 0xffffff is the I/O area reserved for the S1C17 core. Do not access this area ex-

cept when it is required.

Debugger

3.3

Debugging Functions

3.3.1

The debugger provides the following functions:

• Instruction break: A debug interrupt is generated immediately before the set instruction address is executed. An

instruction break can be set at up to four addresses.

• Single step:

A debug interrupt is generated after each instruction has been executed.

• Forcible break: A debug interrupt is generated using an external input signal.

• Software break: A debug interrupt is generated when the brk instruction is executed.

When a debug interrupt occurs, the CPU enters DEBUG mode. The peripheral circuit operations in DEBUG mode

depend on the setting of the DBRUN bit provided in the clock control register of each peripheral circuit. For more

information on the DBRUN bit, refer to “Clock Supply in DEBUG Mode” in each peripheral circuit chapter. DE-

BUG mode continues until a cancel command is sent from the personal computer or the CPU executes the retd in-

struction. Neither hardware interrupts nor NMI are accepted during DEBUG mode.

Resource Requirements and Debugging Tools

3.3.2

Debugging work area

Debugging requires a 64-byte debugging work area. For more information on the work area location, refer to

the “Memory and Bus” chapter. The start address of this debugging work area can be read from the DBRAM

register.