19 Serial communication

RX8130CE

Jump to

ETM50E-07

Seiko Epson Corporation

59

19 Serial communication

19.1 Overview of I

2

C-Bus Interface

The I

2

C-bus supports bi-directional communications via two signal lines: the SDA (data) line and SCL (clock) line. A

combination of these two signals is used to transmit and receive communication start/stop signals, data transfer signals,

acknowledge signals, and so on.

Both the SCL and SDA signals are held at high level whenever communications are not being performed.

The starting and stopping of communications is controlled at the rising edge or falling edge of SDA while SCL is at high

level.

19.2 Data transfers

Data transfers are performed in 8-bit (1 byte) units once the START condition has occurred. There is no limit on the

amount (bytes) of data that are transferred between the START condition and STOP condition.

(However, the transfer time must be no longer than 0.95 seconds.)

19.3 Starting and stopping I

2

C-Bus communications

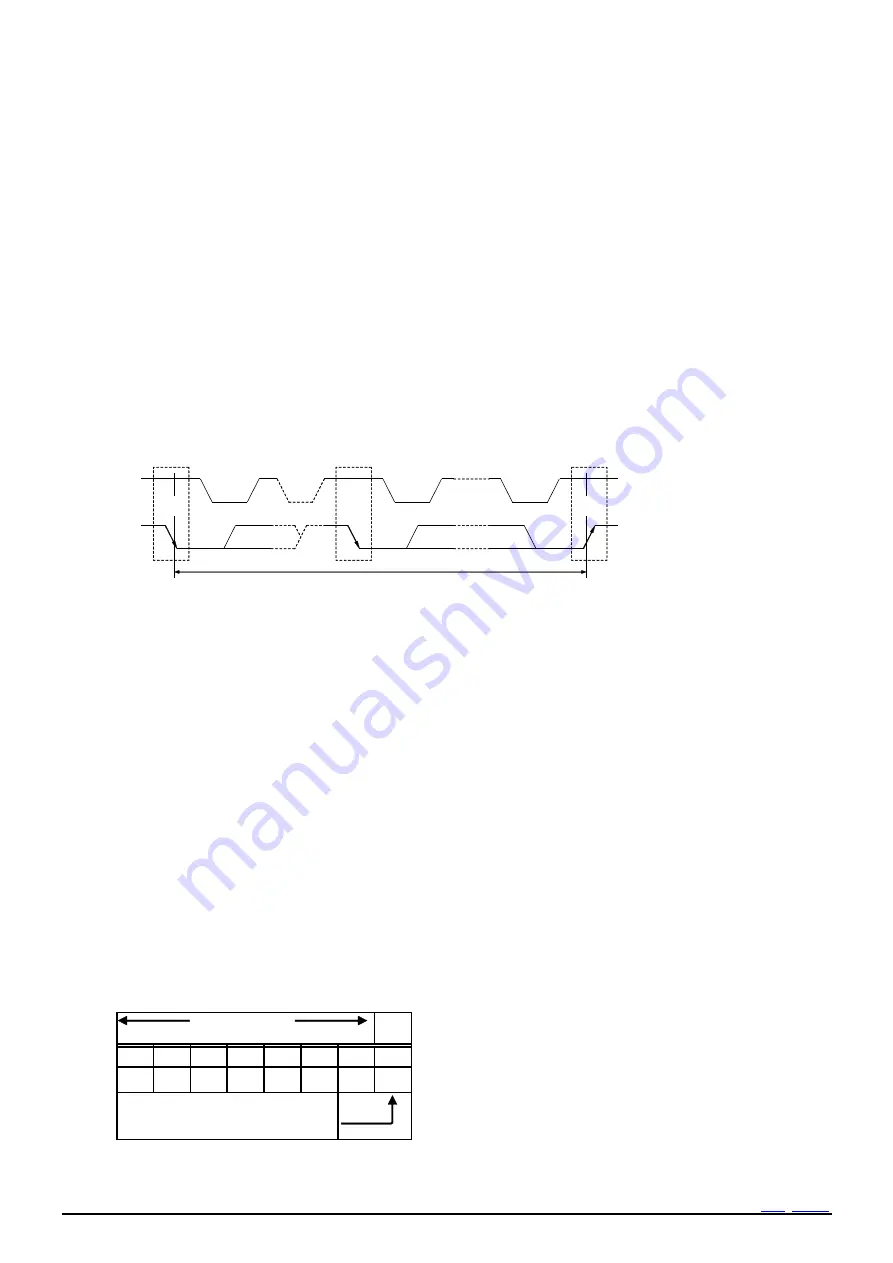

SCL

START

condition

SDA

0.95

s ( Max. )

Repeated START(RESTART)

condition

STOP

condition

[ S ]

[ Sr ]

[ P ]

Figure 47 I

2

C-Bus start/stop timing

1) START condition, repeated START condition, and STOP condition

(1) START condition

The SDA level changes from high to low while SCL is at high level.

(2) STOP condition

This condition regulates how communications on the

I

2

C-Bus are terminated.

The SDA level changes from low to high while SCL is at high level.

(3) Repeated START condition (RESTART condition)

In some cases, the START condition occurs between a previous START condition and the next STOP condition, in

which case the second START condition is distinguished as a RESTART condition. Since the required status is the

same as for the START condition, the SDA level changes from high to low while SCL is at high level.

When accessing this device, all communication from transmitting the start condition to transmitting the stop

condition after access should be completed within 0.95 seconds. If communication requires 0.95 seconds or

longer, the I

2

C bus interface is reset by the internal bus timeout function.

19.4 Slave address

The I

2

C-Bus devices do not have any chip select or chip enable pins. All I

2

C-Bus devices are memorized with a fixed

unique number in it. The chip selection on the I

2

C-Bus is executed, when the interface starts, the master device sends

the required slave address to all devices on the I

2

C-Bus. The receiving device only reacts for interfacing, when the

required slave address is agreed with its own slave address.

During in actual data transmission, the transmitted data contains the slave address and the data with R/W

Slave address

R

/W

bit

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

0

1

1

0

0

1

0

R/W

0 is Write mode

1 is Read mode