14. How to use

RX4111CE

Jump to

ETM62E-02

Seiko Epson Corporation

44

51) EVF bit (Event Flag)

When event occurs, a Time stamp is performed, and EVF is set.

Table 51 EVF bit (Event Flag)

EVF

Data

Description

Write

0

When /INT is outputting Low, it is canceled. It is released to Hi-Z.

1

Ignored

Read

0

Specified interrupt events are not detected.

1

Event occasion is detected.

(The result is retained until this bit is cleared to zero.)

Note: EVF is not set by SPI-Bus command trigger

2) EIE bit (Event Interrupt Enable)

Control of /INT interrupt output when an event occurs (EVF,

"

0

"

"

1

")

.

Table 52 EIE bit (Event Interrupt Enable)

EIE

Data

Description

Write

0

1) When an event interrupt event

occurs, an interrupt signal is not generated

(

/INT status remains Hi-z)

2) When an event interrupt event occurs, the interrupt signal is canceled.

(/INT status changes from low to Hi-z)

1

When an event

interrupt occurs, an interrupt signal is generated (/INT status

changes from Hi-z to low

)

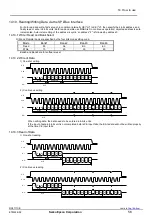

3) OVW bit (Over Write)

Control of

overwriting of Time stamp record

Table 53 OVW bit (Over Write)

OVW

Data

Description

Write

0

The recording is stopped with 8-time stamps, and it is not overwritten.

1

Overwrite available

Figure 34 OVW, pointer operation