ENL-Q6391M2

Sales contact: [email protected] www.enlii.com

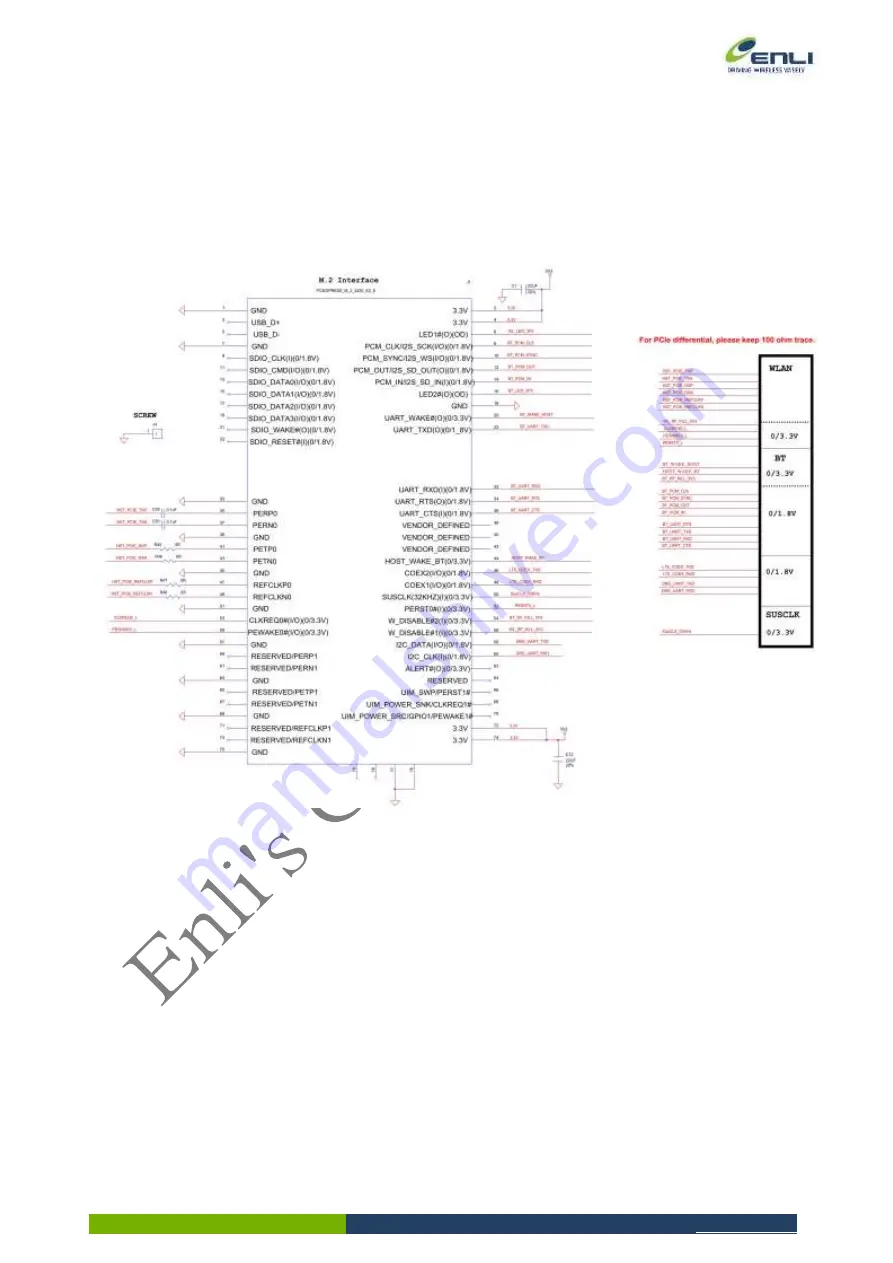

7 Reference Design

7.1 Reference design schematic

Figure 7-1 Reference schematic

C29, C30 should be closed to host.

PCIe differential signals should be followed 100 Ohm impedance.

For the I/O interface voltage, please refer to chapter 4.2 pin definition.

For the 1.8V interface, such as PCM, UART and some I/O, if the host voltage level is

3.3V or 5V, need to add level shift circuit.