126

PSoC CY8CTMG20x and CY8CTST200 TRM, Document No. 001-53603 Rev. *C

I2C Slave

15.3.9

I2C_CFG Register

The I

2

C Configuration Register (I2C_CFG) is used to set the

basic operating modes, baud rate, and selection of inter-

rupts. The bits in this register control baud rate selection and

optional interrupts. The values are typically set once for a

given configuration. The bits in this register are all RW.

Bit 6: PSelect.

Pin Select. With the default value of zero,

the I

2

C pins are P1[7] for clock and P1[5] for data. When this

bit is set, the pins for I

2

C switch to P1[1] for clock and P1[0]

for data. You cannot change this bit while the Enable bit is

set. However, the PSelect bit may be set at the same time

as the enable bits. The two sets of pins used on I

2

C are not

equivalent. The default set, P1[7] and P1[5], are the pre-

ferred set. The alternate set, P1[1] and P1[0], are provided

so that I

2

C may be used with 8-pin PSoC devices.

If In-System Serial Programming (ISSP) is used and the

alternate I

2

C pin set is also used, you must consider the

interaction between the PSoC Test Controller and the I

2

C

bus. The interface requirements for ISSP must be reviewed

to ensure that they are not violated.

Even if ISSP is not used, pins P1[1] and P1[0] respond dif-

ferently than other I/O pins to a POR or XRES event. After

an XRES event, both pins are pulled down to ground by

going into the resistive zero drive mode before reaching the

High Z drive mode. After a POR event, P1[0] drives out a

one, then goes to the resistive zero state for some time, and

finally reaches the High Z drive mode state. After POR,

P1[1] goes into a resistive zero state for a while before going

to the High Z drive mode.

Bit 4: Stop IE.

Stop Interrupt Enable. When this bit is set, a

slave can interrupt upon Stop detection. The status bit asso-

ciated with this interrupt is the Stop Status bit in the

. When the Stop Status bit transitions

from ‘0’ to ‘1’, the interrupt is generated. It is important to

note that the Stop Status bit is not automatically cleared.

Therefore, if it is already set, no new interrupts are gener-

ated until it is cleared by firmware.

Bits 3 and 2: Clock Rate[1:0].

These bits offer a selection

of three sampling and bit rates. All block clocking is based

on the SYSCLK input, which is nominally 12 MHz or 6 MHz

or 24 MHz for CY8CTMG20x and CY8CTST200 (unless the

PSoC device is in external clocking mode). The sampling

rate and the baud rate are determined as follows:

■

Sample Rate = SYSCLK/Prescale Factor

■

Baud Rate = 1/(Sample Rate x Samples per Bit)

When clocking the input with a frequency other than 6/12

MHz (for example, clocking the device with an external

clock), the baud rates and sampling rates scale accordingly.

Whether the block works in a Standard Mode or Fast Mode

system depends upon the sample rate.

The sample rate must be sufficient to resolve bus events,

such as Start and Stop conditions. See the Philips Semicon-

ductors (now NXP Semiconductors) I

2

C-Bus Specification,

version 2.1, for minimum start and stop hold times.

Bit 0: Enable.

When the slave is enabled, the block gener-

ates an interrupt upon any Start condition and an address

byte that it receives indicating the beginning of an I

2

C trans-

fer. When operating as a slave, the block is clocked from an

external master. Therefore, the block works at any fre-

quency up to the maximum defined by the currently selected

clock rate. The internal clock is only used in slave mode, to

ensure that there is adequate setup time from data output to

the next clock upon the release of a slave stall. When the

Enable bit is ‘0’, the block is held in reset and all status is

cleared. CPU access to the HW buffer (EZI2C mode) is

blocked when the bit is '0'. Block enable is synchronized to

the SYSCLK clock input (

). If the block is enabled when there is an I

2

C

transaction already on the I

2

C bus, an erroneous start is

detected if SCL is high and SDA is low. (SDA in this case is

low because of a data/ack bit.) Thus, to avoid this erroneous

start detection, enable the block only when the bus is idle

(SCL and SDA are high when idle) or only when both SCL

and SDA are low.

The other option is to change the drive modes of the I

2

C

pins to be other than open drain mode and then enable the

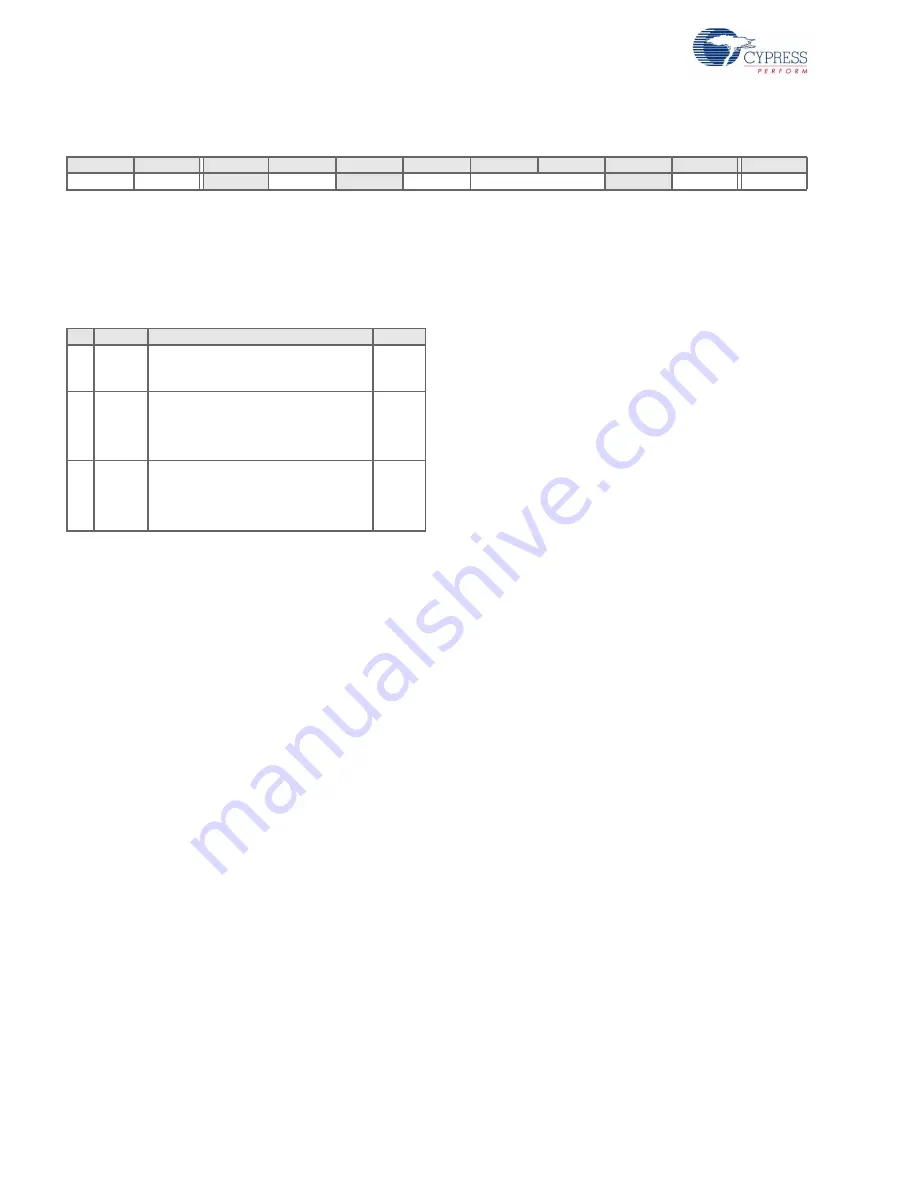

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

0,D6h

PSelect

Stop IE

Clock Rate[1:0]

Enable

RW : 00

Table 15-1. I2C_CFG Configuration Register

Bit

Access

Description

Mode

6

RW

I2C Pin Select

0 = P1[7], P1[5]

1 = P1[1], P1[0]

Slave

4

RW

Stop IE

Stop interrupt enable.

0 = Disabled.

1 = Enabled. An interrupt is generated upon

the detection of a Stop condition.

Slave

3:2

RW

Clock Rate

00 = 100K Standard Mode

01 = 400K Fast Mode

10 = 50K Standard Mode

11 = Reserved

Slave

Содержание PSoC CY8CTMG20 Series

Страница 4: ...4 Contents Overview Feedback...

Страница 26: ...26 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Section B PSoC Core Feedback...

Страница 54: ...54 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Interrupt Controller Feedback...

Страница 62: ...62 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C General Purpose I O GPIO Feedback...

Страница 82: ...82 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Sleep and Watchdog Feedback...

Страница 134: ...134 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C I2C Slave Feedback...

Страница 142: ...142 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C System Resets Feedback...

Страница 160: ...160 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C SPI Feedback...

Страница 182: ...182 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Full Speed USB Feedback...

Страница 186: ...186 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Section E Registers Feedback...

Страница 302: ...302 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Glossary Feedback...