CY8C28xxx PSoC Programmable System-on-Chip TRM, Document No. 001-52594 Rev. *G

217

CPU_SCR0

x,FFh

13.2.82

CPU_SCR0

System Status and Control Register 0

This register is used to convey the status and control of events for various functions of a PSoC device.

In the table, note that reserved bits are grayed table cells and are not described in the bit description section. Reserved bits

should always be written with a value of ‘0’. For additional information, refer to the

“Register Definitions” on page 99

in the

Sleep and Watchdog chapter.

7

GIES

Global interrupt enable status. It is recommended that the user read the Global Interrupt Enable Flag

bit from the

. This bit is Read Only for GIES. Its use is discouraged, as

the Flag register is now readable at address x,F7h (read only).

5

WDRS

Watchdog Reset Status. This bit may not be set by user code; however, it may be cleared by writing it

with a ‘0’.

0

No Watchdog Reset has occurred.

1

Watchdog Reset has occurred.

4

PORS

Power On Reset Status. This bit may not be set by user code; however, it may be cleared by writing it

with a ‘0’.

0

Power On Reset has not occurred and watchdog timer is enabled.

1

Will be set after external reset or Power On Reset.

3

Sleep

Set by the user to enable the CPU sleep state. CPU will remain in Sleep mode until any interrupt is

pending.

0

Normal operation

1

Sleep

0

STOP

0

M8C is free to execute code.

1

M8C is halted. Can only be cleared by POR, XRES, or WDR.

Individual Register Names and Addresses:

x,FFh

CPU_SCR0: x,FFh

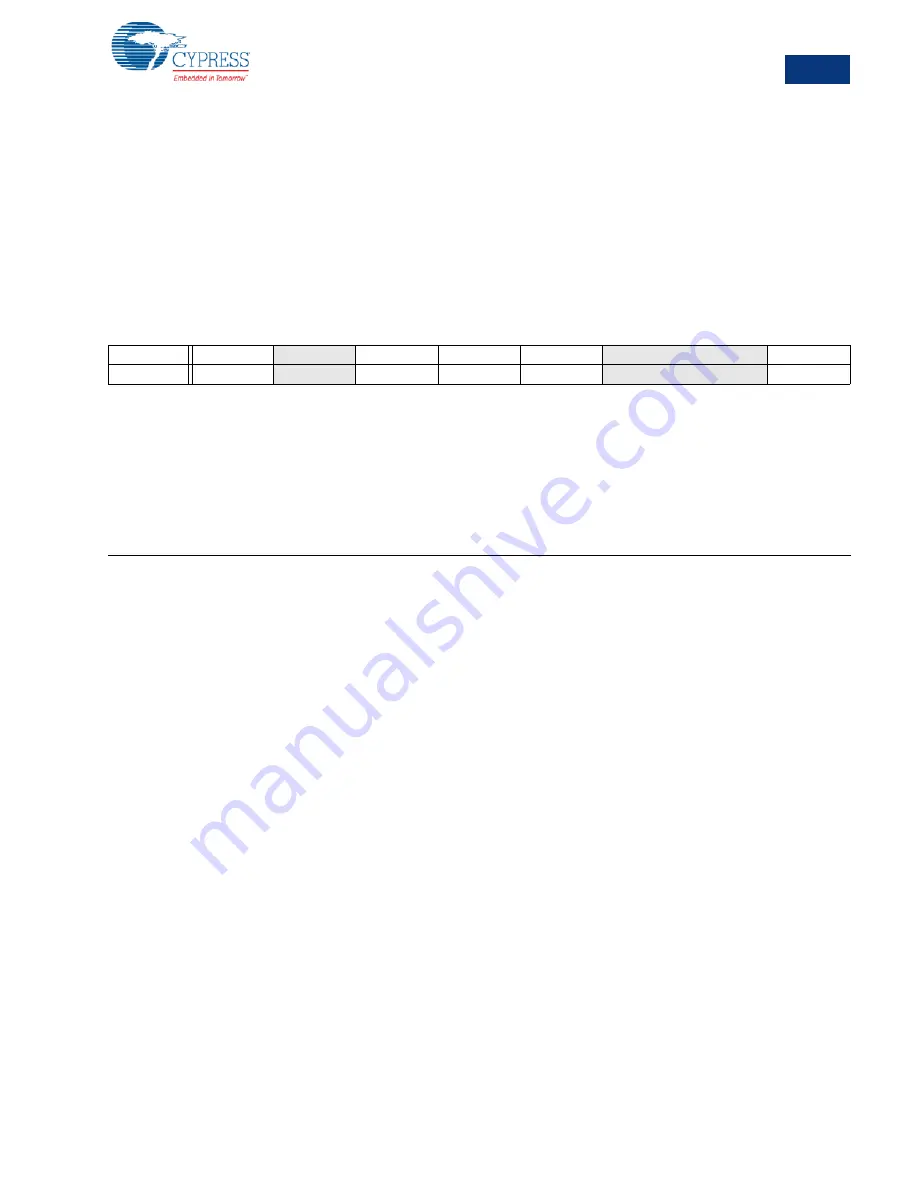

7

6

5

4

3

2

1

0

Access : POR

R : 0

RC : 0

RC : 1

RW : 0

RW : 0

Bit Name

GIES

WDRS

PORS

Sleep

STOP

Bit

Name

Description

Содержание CY8C28 series

Страница 65: ...64 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G RAM Paging ...

Страница 85: ...84 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Internal Main Oscillator IMO ...

Страница 93: ...92 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G External Crystal Oscillator ECO ...

Страница 97: ...96 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Phase Locked Loop PLL ...

Страница 125: ...124 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 311: ...310 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G IDAC_CR0 1 FDh ...

Страница 317: ...316 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 393: ...392 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...

Страница 425: ...424 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Analog Reference ...

Страница 461: ...460 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Two Column Limited Analog System ...

Страница 477: ...476 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Digital Clocks ...

Страница 483: ...482 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Multiply Accumulate MAC ...

Страница 513: ...512 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Internal Voltage Reference ...

Страница 523: ...522 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Switch Mode Pump SMP ...

Страница 533: ...532 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G I O Analog Multiplexer ...

Страница 537: ...536 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G Real Time Clock RTC ...

Страница 561: ...560 CY8C28xxx PSoC Programmable System on Chip TRM Document No 001 52594 Rev G ...