CMT2300A

Rev 1.0 | Page24/46

www.cmostek.com

be automatically calibrated during power on and will be periodically calibrated since then. These calibrations will keep the

frequency tolerance of the oscillator 1%.

4.3.4 Low Battery Detection

The chip sets up low voltage detection.When the chip is tuned to a certain frequency, the test is performed once.Frequency

tuning occurs when the chip jumps from the SLEEP/STBY state to the RFS/TFS/TX/RX state. The result can be read by the

LBD_VALUE register.

4.3.5 Received Signal Strength Indicator(RSSI)

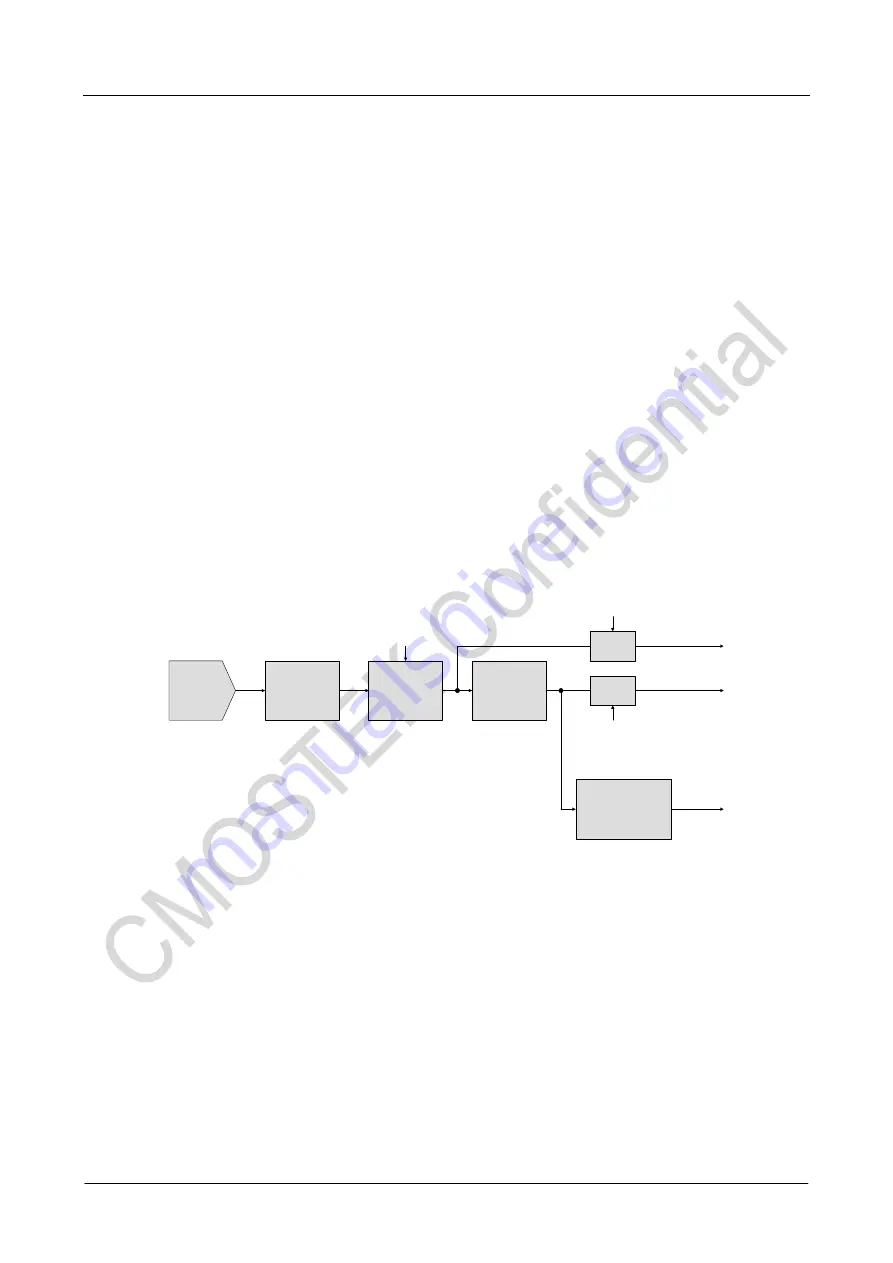

RSSI is used to evaluate the signal strengthinside the channel. The cascaded I/Q logarithmic amplifier amplifies the signal before

it is sent to the demodulator. The logarithmic amplifier of I channels and Q channel contains the received signal indicator, in which

the DC voltage is generated is proportional to the input signal strength. The output of RSSI is the sum of thevalues of the two

channels’ signals. The output has 80dB dynamic range above the sensitivity. After the RSSI output is sampled by the ADC and

filtered by a SAR FILTER and a RSSI AVG FILTER. The order of the average filter can be set by RSSI_AVG_MODE<2:0>. The

code value is translated into dBm value after filtering. Users can read the registerRSSI_CODE<7:0> to obtain the RSSI code

value, or RSSI_DBM<7:0> to obtain the dBm value. By setting the register RSSI_DET_SEL<1:0> Users can determine whether

the RSSI is output to the MCU in real time, or latched at the instance when the preamble, sync, or the whole packet is received.

Also, CMT2300A allows the user to setup a threshold by RSSI_TRIG_TH<7:0> to compare with the real-time RSSI value. If the

RSSI is larger than the threshold it outputs logic 1, otherwise outputs logic 0. The output can be used as a source of the RSSI

VLD interrupt, ofthe receive time extending condition in the super low power (SLP) mode.

SAR

FILTER

CODE to dBm

CONVERT

SAR

ADC

RSSI AVG

FILTER

RSSI_CODE<7:0>

RSSI_DBM<7:0>

RSSI_AVG_MODE<2:0>

COMPARE to

RSSI_TRIG_TH<7:0>

RESULT

LATCH

LATCH

RSSI_DET_SEL<1:0>

RSSI_DET_SEL<1:0>

Figure 7. RSSI detection and comparison circuit

CMT2300A has done a certain degree of calibration before delivery. In order to obtain more accurate RSSI measurement results,

the user needs to recalibrate the RSSI circuit in their dedicated applications. For further information, please refer to the

“AN144-CMT2300AW RSSI Usage Guideline”.

4.3.6 Phase Jump Detector

(

PJD

)

PJD is Phase Jump Detector. When the chip is in FSK demodulation, itcan automatically observe the phase jump characteristics

of the received signal to determine whether it is awanted signal or an unwanted noise.